|

Архитектура AVR:

развитие вширь и вглубь. Часть 1

В январе 2007 года корпорация ATMEL провела в Норвегии, на родине AVR, традиционный дистрибьюторский семинар, посвященный новым достижениям в AVR-строении. Развитие AVR-контроллеров происходит по трем основным направлениям: микросхемы для автомобильных применений, микросхемы со сверхнизким энергопотреблением (picoPower) и микросхемы, построенные на принципиально новом высокопроизводительном низкопотребляющем 32-разрядном ядре AVR32. В первой части статьи приводится обзор основных характеристик новинок. Во второй части более подробно будет рассмотрено семейство контроллеров AVR32 с Flash-ПЗУ на кристалле.

Автомобильные AVR-контроллеры

Для применения в автомобильной промышленности ATMEL разработала «высокотемпературные» версии микросхем. Следует отметить, что это не «отобранные» стандартные кристаллы, а специально разработанная топология. Особое внимание уделено модулю Flash-памяти. Известно, что время хранения информации, записанной во Flash-память, обратно пропорционально температуре кристалла. Таким образом, для микросхемы любого производителя фактический срок хранения данных в памяти при комнатной температуре и при температуре, например, +85 °C, отличается в несколько раз. Инженеры копрорации ATMEL разработали специальную топологию элемента FLASH-памяти со сниженными токами утечки. В результате гарантируется надежная работа микросхем в диапазоне температур от –40 до +125 °C. Существует четыре градации диапазонов рабочих температур для микросхем автомобильного применения:

- Grade 3, –40...+85 °C — индекс в названии микросхемы Т;

- Grade 2, –40...+105 °C — индекс в названии микросхемы Т1;

- Grade 1, –40...+125 °C — индекс в названии микросхемы Z;

- Grade 0, –40...+150 °C — индекс в названии микросхемы Т2.

Пилотной микросхемой на «автомобильный» температурный диапазон стала ATmega88.

В настоящее время список микросхем расширен, а специальная версия ATmega88-ERSAT2 может работать в диапазоне от –40 до +150 °C! Основные параметры микросхем приведены в таблице 1.

Таблица 1. Основные параметры микросхем фирмы ATMEL

| |

Flash

кбайт |

EEPROM

байт |

SRAM

байт |

16-раз-

рядный

таймер |

8-раз-

рядный

таймер |

ШИМ-каналы |

RTC |

SPI |

UART |

TWI |

Умно-

житель |

Преры-

вания |

Внеш-

ние

преры-

вания |

Тип корпуса |

AT90CAN128 AT90CAN128 |

128 |

4096 |

4096 |

2 |

2 |

8 |

+ |

+ |

2 |

- |

+ |

34 |

8 |

LQFP/MLF64 |

AT90CAN32 AT90CAN32 |

32 |

1024 |

2048 |

2 |

2 |

8 |

+ |

+ |

2 |

- |

+ |

34 |

8 |

LQFP/MLF64 |

AT90CAN64 AT90CAN64 |

64 |

2048 |

4096 |

2 |

2 |

8 |

+ |

+ |

2 |

- |

+ |

34 |

8 |

LQFP/MLF64 |

|

ATtiny25 ATtiny25 |

2 |

128 |

128 |

- |

2 |

4 |

- |

USI |

- |

USI |

- |

15 |

7 |

Узкий SOIC 8 |

ATtiny45 ATtiny45 |

4 |

256 |

256 |

- |

2 |

4 |

- |

USI |

- |

USI |

- |

15 |

7 |

Узкий SOIC 8 |

ATtiny85 ATtiny85 |

8 |

512 |

512 |

- |

2 |

4 |

- |

USI |

- |

USI |

- |

15 |

7 |

Узкий SOIC 8 |

ATmega48 ATmega48 |

4 |

256 |

512 |

1 |

2 |

6 |

+ |

1+USART |

1 |

+ |

+ |

26 |

26 |

TQFP/QFN32 |

ATmega88 ATmega88 |

8 |

512 |

1024 |

1 |

2 |

6 |

+ |

1+USART |

1 |

+ |

+ |

26 |

26 |

TQFP/QFN32 |

ATmega168 ATmega168 |

16 |

512 |

1024 |

1 |

2 |

6 |

+ |

1+USART |

1 |

+ |

+ |

26 |

26 |

TQFP/QFN32 |

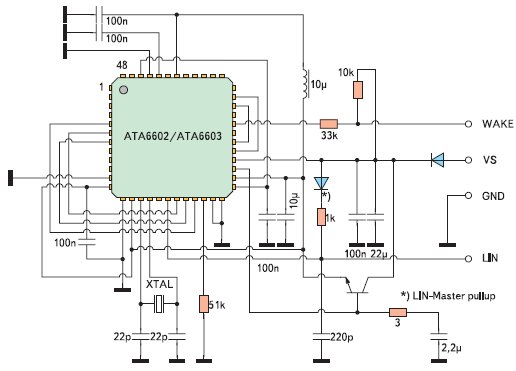

Еще одним интересным решением для применения в автомобильной промышленности является микросхема, содержащим в корпусе два кристалла — AVR-контроллер и модуль интерфейса LIN. Микросхема функционирует в диапазоне напряжений питания от 5 до 18 В. Типовая схема включения микросхемы приведена на рис. 1.

Рис. 1. Схема включения контроллера ATA6602/6603

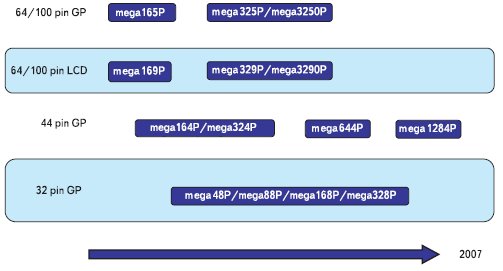

К концу 2007 года будет выпущено более 10 типов микросхем с расширенным диапазоном рабочих температур (рис. 2).

Рис. 2. Программа развития микроконтролеров серии «automotive»

Технология picoPower

С момента появления на рынке в 1997 году контроллеры AVR отличались невысоким энергопотреблением. Для управления потребляемой мощностью контроллер имеет шесть режимов энергосбережения:

- Idle mode — в этом режиме блокируется подача тактовых импульсов на CPU и Flash-память.

- ADC noise reduction mode — Idle mode, плюс блокируется тактирование портов ввода–вывода.

- Extended Standby mode — ADC noise reduction mode, плюс запрещается работа АЦП и EEPROM.

- Standby mode — Extended Standby mode, плюс запрещается работа таймера 2.

- Power Down mode — Standby mode, плюс запрещается работа генератора.

- Power Save mode — самый низкопотребляющий режим, активны только асинхронные модули — прерывания и порт TWI.

В 2006 году компания анонсировала разработку новых экономичных AVR-контроллеров семейства picoPower. В этом семействе реализован ряд дополнительных мер со снижению энергопотребления как в режиме ожидания, так и в активном режиме. Ниже более подробно рассмотрены особенности нового семейства.

Питание 1,8 В для всех модулей кристалла. В отличие от микроконтроллеров прежних поколений, технология picoPower подразумевает напряжение 1,8 В для питания абсолютно всех модулей кристалла, включая аналоговые модули (АЦП, компаратор, источник опорного напряжения), а также модулей памяти (Flash-ПЗУ, EEPROM и ОЗУ).

Концепция «спящий BOD». Практически все современные микроконтроллеры имеют на кристалле модуль слежения за уровнем напряжения питания — BOD (Brown Out Detector). Есть два подхода к снижению потребления этого модуля. Первый — сделать модуль очень экономичным. Плата за экономичность — резкое, до единиц миллисекунд, снижение быстродействия. Второй — использовать быстродействующий BOD, однако отключать этот модуль на время пребывания контроллера в режиме ожидания. При этом время срабатывания модуля составляет 2 мкс. Естественно, для надежной работы контроллера модуль BOD отключается после перехода в режим ожидания, а включается до выхода из этого режима.

Ультранизкопотребляющий генератор на 32 кГц. При переходе контроллера в режим Standby существенную долю общего потребления контроллера составляют цепи генератора. Применение новой версии модуля генератора, работающего с «часовым» кварцем, позволяет получить ток не более 650 нА с учетом работающего модуля BOD. Это лучший на сегодня показатель в промышленности.

Минимизация токов утечки. Потребление тока в режимах энергосбережения в большей степени определяется токами утечки кристалла. Применение собственного процесса для изготовления кристаллов по технологии picoPower позволяет получить токи утечки в режиме Standby при напряжении питания 1,8 В не более 100 нА.

Дальнейшие меры по снижению энергопотребления относятся к работе периферийных узлов в активном режиме. Как известно, потребление КМДП-микросхем в активном режиме напрямую зависит от частоты переключения вентилей вследствие перезаряда паразитных емкостей кристалла. Таким образом, если запретить подачу тактовых импульсов на некоторые модули контроллера, можно снизить потребляемую мощность. Эта технология получила название Clock Gating. Существует три уровня работы Clock Gating. Кристалл разделен на три энергопотребителя — Analog Domain, CPU Domain и In/Out Domain. Первый уровень отвечает за тактирование каждого энергопотребителя в зависимости от текущего режима работы контроллера.

Второй уровень задается программированием специального регистра снижения потребляемой мощности (Power Reduction Register, PRR). Известно, что в конкретной программе, выполняемой контроллером, не все периферийные модули могут быть активными постоянно. Некоторые модули задействуются на определенные интервалы времени, а какие-то — вообще не используются при выполнении той или иной процедуры. Регистр PRR управляет включением-выключением периферийных модулей.

При отключении модуля его текущий статус запоминается, и все его регистры становятся недоступными для модификации. Как показывает стастистика, использование такого механизма позволяет снизить суммарную потребляемую мощность на 5–10% в активном режиме и на 10–20% в режиме Idle.

Третий уровень Clock Gating отвечает за адаптивное тактирование регистров. Известно, что не все регистры модифицируются в каждом такте. Таким образом, можно не подавать тактирующие импульсы на регистры, состояние которых не требуется модифицировать в данном цикле процессора.

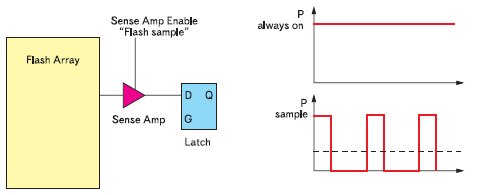

Снижение потребления модуля Flash-памяти. Flash-память — это, по существу, аналоговый блок со статическим энергопотреблением. Как правило, во время работы контроллера этот блок всегда активен. Следует учесть, однако, что в ряде случаев контроллер используется не на максимальной тактовой частоте, следовательно, время выборки команды из Flash-ПЗУ меньше одного периода тактовой частоты. Когда AVR-контроллер работает на частоте не выше нескольких мегагерц, используется техника «Flash sampling» — модуль памяти активизируется только на время, необходимое для выборки команды, а затем отключается. Этот алгоритм проиллюстрирован на рис. 3.

Рис. 3. Работа системы «Flash sampling»

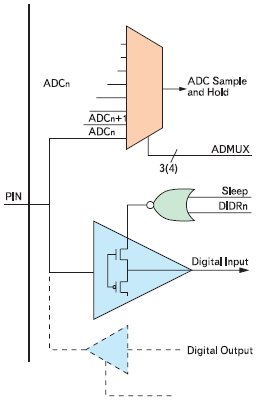

Снижение токов утечки по входам. Многие AVR-контроллеры имеют модуль АЦП, который использует некоторые порты как аналоговые входы (рис. 4).

Рис. 4. Структура универсального порта ввода–вывода

Мультиплексирование выводов контроллера для цифровых или аналоговых операций повышает функциональность, однако приводит к увеличению энергопотребления. Это объясняется следующим. Входной каскад КМДП-логики состоит из двух комплементарных МДП-транзисторов. При изменении уровня входного напряжения, в моменты, когда на вход подается уровень, примерно равный половине питания, оба транзистора «приоткрыты», и через входной каскад протекает сквозной ток. Для цифровых сигналов с крутыми фронтами это время пренебрежимо мало, однако если вывод используется как вход АЦП, на нем «неудобное» напряжение может оставаться сколь угодно долгое время, что приводит к увеличению уровня потребляемого тока. Для снижения потребления нужно отключать цифровой вход на время работы АЦП. Для этого введен специальный регистр DIDR (Dedicated Input Disable Register), который выборочно запрещает цифровые входы при работе АЦП.

Также этот регистр запрещает неиспользуемые входы контроллера при переходе в ждущий режим.

Таким образом, совокупность мер по уменьшению тока потребления как в активном режиме, так и в режимах ожидания позволила создать производительный процессор, который отличается весьма малыми токами потребления.

Архитектура AVR32

Большую долю рынка 32-разрядных контроллеров в настоящее время захватили микросхемы на базе ядер ARM7, ARM9 и ARM11. ATMEL также производит контроллеры на базе ядер ARM7 и ARM9. Несмотря на это, в 2001 году корпорация начала разработку принципиально новой 32-разрядной RISC-архитектуры. Основной целью было повышение вычислительной производительности за такт процессора. Задача формулировалась как разработка процессора, который сможет решать сложные задачи цифровой обработки информации при малом потреблении энергии — требование разработчиков мобильных устройств. Ядро должно одновременно выполнять задачи MPU и DSP в рамках одной программной и инструментальной базы. В дополнение к производительному ядру контроллеры нового поколения имеют высокоскоростную периферию, в частности, два контроллера 10/100 Mbps MAC и High-Speed USB (480 Mbps). В последующих версиях контроллеров будет добавлет хост-контроллер USB (480 Mbps), поддерживающий режим OTG (On The Go).

Основные параметры микросхем приведены в таблице 2.

Таблица 2. Основные параметры микросхем AT32AP700X

| |

SDRAM (кбайт) |

DSP

инст-

рук-

ции |

Век-

тор-

ный

со-

про-

цес-

сор |

Ether-

net 10/ 100 MAC |

USB HS Devi-

ce |

Конт-

рол-

лер

LCD 2048 x 2048 |

Число выво-

дов общего назна-

чения |

Число DMA кана-

лов |

Интер-

фейс внеш-

ней шины |

Конт-

роллер SDRAM |

AC97 |

Интер-

фейс к камере |

ФАПЧ |

Квар-

цевый осцил-

лятор |

MMU/ MPU |

Бес-свинцовый корпус |

AT32AP7000 AT32AP7000 |

32 |

+ |

+ |

2 |

1 |

24бит |

160 |

20 |

+ |

+ |

1 |

CMOS |

2 |

2 |

MMU |

256 CTBGA |

| AT3AP7001 |

32 |

+ |

+ |

0 |

1 |

- |

90 |

20 |

+ |

+ |

1 |

CMOS |

2 |

2 |

MMU |

208 VQFP |

| AT32AP7002 |

32 |

+ |

+ |

0 |

1 |

18бит |

85 |

20 |

+ |

+ |

1 |

CMOS |

2 |

2 |

MMU |

196 CTBGA |

Архитектура AVR32 разработана в норвежском городе Тронхейм, там же, где созданы 8-разрядные AVR-контроллеры. В разработке участвовала команда из двадцати инженеров и программистов. В результате 4-летней работы над такими алгоритмами, как вычисление суммы абсолютных разностей (SAD) и обратное дискретное косинусное преобразование (IDCP), был достигнут 35% прирост эффективности на один такт процессора по сравнению с ядром ARM11. Это означает возможность декодировать в реальном времени видеофрагмент MPEG-4 разрешением QVGA с частой 30 кадров в секунду при частоте ядра 100 MГц, в то время как ARM11 для решения этой задачи требуется частота 150–170 MГц.

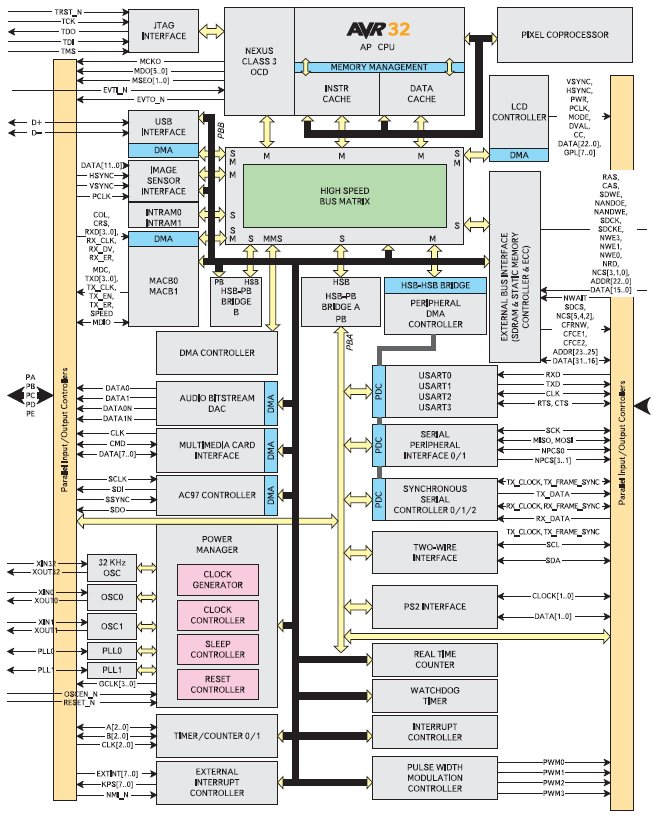

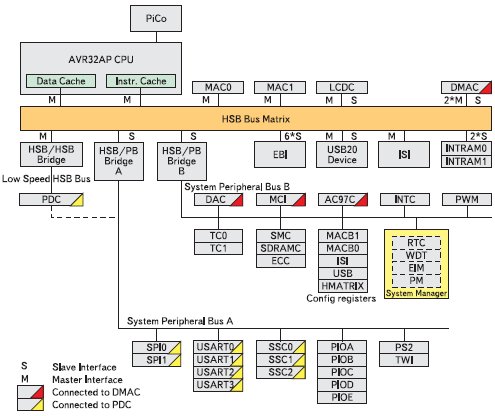

Структурная схема первого представителя AVR32 — контроллера AT32AP7000 приведена на рис. 5.

Рис. 5. Структурная схема контроллера AT32AP7000

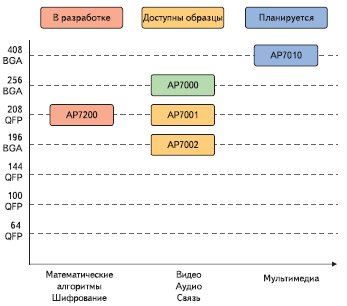

На ядре AVR32 разрабатывается семейство контроллеров с аббревиатурой AP (Application Processor). Микросхемы будут выпускаться в корпусах BGA и TQFP. На рис. 6. представлена программа развития этого семейства.

Рис. 6. Планы развития AVR32

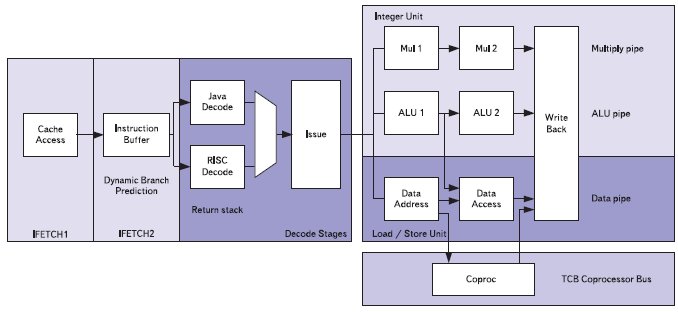

Структурная схема конвейера AVR32

Основой архитектуры AVR32 является семистадийный конвейер (рис. 7), обеспечивающий высокую производительность. Семистадийный конвейер AVR32 состоит из трех модулей, подготавливающих команду и четырех модулей, производящих выполнение.

Рис. 7. Схема конвейера AVR32

На первом этапе инструкции выбираются из кэш-памяти.

На втором этапе происходит динамическое предсказание ветвления на основе предыдущего значения, далее инструкции перемещаются в буфер декодера Java или RISC команд. Механизм предсказания ветвления позволяет избегать перезагрузки конвейера при выполнении операций ветвления. При предсказании ветвления в кэш загружается следующая за ветвлением операция.

Совместно с высокой плотностью кода это позволяет снизить использование памяти и производить переходы без потери циклов.

Третий этап — декодирование команды. В зависимости от содержания команды она попадает в целочисленный модуль, который состоит из трех конвейеров:

- конвейер умножения, состоящий из двух блоков умножения;

- конвейер АЛУ, состоящий из двух блоков вычислений;

- конвейер данных, состоящий из модуля адресации и модуля доступа к данным.

Конвейер данных имеет доступ к сопроцессору для параллельного выполнения матричных и векторных операций.

Три перечисленных конвейера поддерживают одновременное исполнение независимых инструкций с изменением последовательности (рис. 8). То есть, например, пока модуль умножения в течение 32 тактов занят, в модуле АЛУ может выполняться следующая операция.

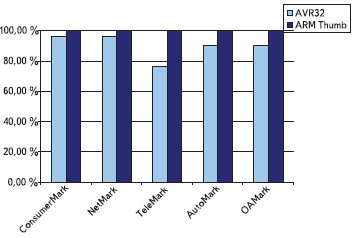

Рис. 8. Плотность кода AVR32 AP в тестах EEMBC (оптимизация по скорости)

Оптимизация доступа к памяти

Конвейеры соединены шинами, позволяющими передавать данные непосредственно от одного модуля к другому без загрузки дополнительных ресурсов. Например, результат суммирования из блока АЛУ2 сразу после завершения выполнения операции пересылается на вход модуля умножения 1, АЛУ1 и блок адресации данных (Data Address). Такой механизм позволяет экономить 3 такта, которые требуются для программной пересылки данных на вход конвейера (рис. 9).

Рис. 9. Плотность кода AVR32 AP в тестах EEMBC (оптимизация по длине)

Работа с сопроцессором реализована через конвейер данных, что минимизирует задержки во время выполнения команд сопроцессором.

Оптимизация на уровне буфера команд за счет переменной длины команд

AVR32 работает с расширенным набором RISC-команд. Команды могут иметь длину 16 или 32 бита и следовать общим потоком. В отличие от архитектуры ARM, у этого ядра нет необходимости переключаться между двумя режимами. Все команды распознаются непосредственно в конвейере.

SIMD инструкции

В набор команд AVR32 входят инструкции для операций с множественными данными (Single Instruction Multiply Data), позволяющие в четыре раза увеличить производительность некоторых DSP алгоритмов, которые требуют выполнения одинаковых операций с потоком данных. Например, при декодировании видео формата MPEG производится расчет восьмибитных сумм абсолютных разностей (SAD). Для этого четыре 8-битных пикселя загружаются из памяти одной операцией, затем выполняется пакетное вычитание беззнаковых байтов с проверкой переопустошения, сложение байтов внутри старшей и младшей пар и распаковка их в полуслова.

Затем для вычисления значения SAD все значения складываются.

Инструкции эффективного доступа к памяти

В среднем около 30% процессорного времени уходит не на обработку данных, а на инструкции чтения-записи. Архитектура AVR32 уменьшает число требуемых циклов для инструкций чтения-записи байта (8 разрядов), полуслова (16 разрядов), слова (32 разряда) и двойного слова (64 разряда), совмещая их с арифметическими операциями над указателем и ускоряя таким образом скорость доступа к данным в таблицах, структурах и случайно расположенным данных, которые потребуются в ближайших последующих циклах.

Широко применяемые алгоритмы блочного кодирования, такие как Blowfish и Triple-DES, используют таблицы подстановок, для работы с которыми в современных МК требуется большое число тактов процессора. Например, выполнение следующей операции:

result=ptr0[offset0>>24]^ptr1[(offset1>>16)&0xff]^ptr2[(offset2>>

8)&0xff]^ptr3[offset3&0xff];

В основе лежат четыре операции доступа к памяти, извлекающие один из четырех байтов 32-разрядного слова. Результатом операции является адрес памяти, к которому требуется доступ.

Для выполнения этой операции на МК с традиционной RISC-архитектурой потребуется 14 тактов. AVR32 выполнит эту операцию всего за 7 тактов. Использование инструкции чтения с извлеченным индексом (extracted index) позволяет ядру AVR32 выполнить все четыре операции доступа к памяти за четыре такта, сохраняя при этом все четыре смещения в одном регистре.

За счет уменьшения числа требуемых инструкций для выполнения операций увеличивается производительность ядра AVR32.

DSP-инструкции

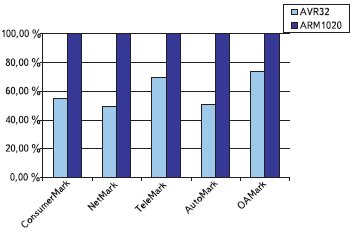

В набор команд входят DSP-команды, такие как битовые операции, умножение с накоплением (МАС), сдвиг на любое число битов за один такт, быстрые масочные операции с битами в слове и многое другое. Такое нововведение позволяет не только быстро выполнять операции с портами общего назначения. Появляется возможность выполнять потоковую обработку данных на кристалле, Фурье-анализ, кодирование-декодирование, распознавание образов, воспроизведение аудио и видео без использования внешних кодеков (рис. 10).

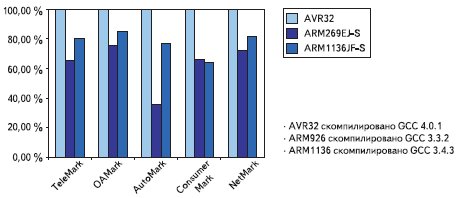

Рис. 10. Сравнительная производительность AVR32

Аппаратное выполнение Java-инструкций

В конвейере AVR32 реализована аппаратная поддержка виртуальной машины Java— то есть кроме RISC-инструкций ядро может выполнять большинство инструкций байткода Java. Использование Java увеличивает возможности по использованию существующих пользовательских приложений и позволяет сократить время на перенос существующих или разработку новых приложений.

В отличие от программной Java-машины, использование аппаратных возможностей позволяет в несколько раз повысить скорость выполнения. Вполне вероятно, что программы для контроллеров класса AVR32 через несколько лет будут разрабатываться на Java.

Разветвленная шинная топология и энергопотребление

Применение в AP7000 многослойной разветвленной архитектуры системных шин (рис. 11) позволяет распараллеливать операции передачи данных, а два независимых периферийных контроллера, работающие на разных частотах, физически разделяют высокоскоростную и медленную периферию. Таким образом, не тратится дополнительная энергия при работе медленных периферийных модулей на высокой частоте.

Рис. 11. Схема шин и периферии AP7000

Контроллер разделен на четыре домена— ядро и шинная матрица (HBUS Matrix) и два периферийных контроллера, в каждом из которых частота может быть установлена независимо.

Поддержка компиляторов и ОС

Архитектура AVR32 разрабатывалась при тесном сотрудничестве с компанией IAR, которая занимается разработкой компиляторов для микроконтроллеров. Это выразилось в более удобной для компилятора архитектуре регистров. Также на этапе разработки было заложено требование по поддержке и оптимизации на уровне архитектуры использования операцилннй системы (ОС) для AVR32. В качестве ОС выбрана Linux. Существует специальный механизм, ускоряющий переключение между процессами и выполнение некоторых часто используемых системных вызовов. Естественно, во всех микроконтроллерах семейства AP7000 присутствует модуль MMU. Разработку программного обеспечения для AVR32 можно вести с применением компилятора GCC. Также в разработке находится порт Linux под AVR32.

Таким образом, микроконтроллер AT32 AP7000, построенный на новом ядре AVR32, предоставляет возможности по высокоскоростному вводу и передаче данных, выводу информации на ЖК-дисплей, потоковой обработке. При этом AP7000 остается микроконтроллером с низким потреблением, которое на 80% связано с архитектурными особенностями семейства AVR32.

В дополнение к семейству AVR32 AP (Application Processor) будут выпущены микросхемы семейства uC (MicroController). Эти микросхемы являются упрощенной версией AP с точки зрения насыщенности интерфейсными модулями, однако они содержат на кристалле Flash-ПЗУ и ОЗУ, что позволит создавать на них компактные недорогие одноплатные решения. Об этом — вторая часть статьи.

Николай КОРОЛЕВ

Антон ШАБЫНИН

|