|

Первый среди равных. Микроконтроллер Cyan Technology eCOG1. Часть N 1

Разговоры о необходимости и важности микроконтроллеров в современной жизни уже перестали быть актуальными: без них немыслимо ни современное производство, ни окружающая нас техника . Современный рынок микроконтроллеров позволяет решать практически любые проблемы, вопрос только в выборе наиболее подходящего.

Развитие микроконтроллеров в настоящее время идет, во-первых, по пути снижения энергопотребления (резко возросла доля мобильных устройств), во-вторых, по пути повышения функциональности микроконтроллеров. Одним из лидеров этого направления является компания Cyan Technology, выпустившая микроконтроллер eCOG1, фактически первый среди равных в своей «весовой категории».

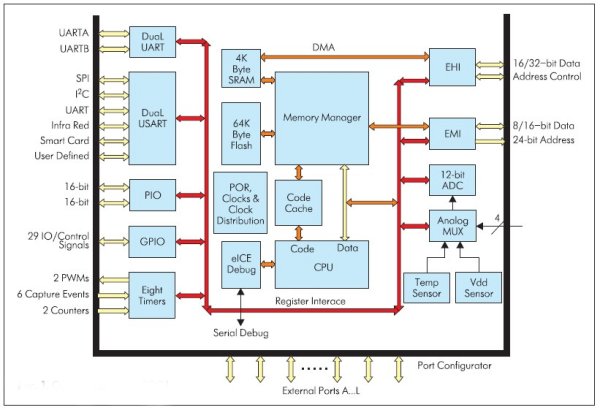

Рисунок 1. Структурная схема eCOG1

eCOG1 представляет собой 16-разрядный микроконтроллер (рис. 1), выполненный на основе гарвардской архитектуры с 24-разрядным линейным адресным пространством команд (32 Мбайта) и 16-разрядным, тоже линейным, адресным пространством данных (128 кбайт). К этому надо добавить встроенную Flash-память на 64 Кбайт и статическое ОЗУ на 6 кбайт. Минимальное потребление (таблица 1) не может не порадовать разработчиков мобильных и автономных систем.

Таблица 1. Потребление eCOG1 в различных режимах работы.

| Режим работы, тактовая частота |

Номинальное значение тока потребления |

Единица измерения |

| Выполнение команд, 25 МГц |

11 |

мА |

| Выполнение команд, 2,5 МГц |

1,1 |

мА |

| Выполнение команд, 16 кГц |

10,1 |

мкА |

| Ждущий режим |

0,4 |

мкА |

Но на этом список особенностей микроконтроллера eCOG1 не заканчивается. Вкратце перечислим остальные.

- Векторные прерывания, набор регистров прерываний, выполнение большинства команд за один цикл.

- Набор мощных команд, включая арифметические операции, гибкие режимы адресации и перемещения данных из регистра в регистр.

- Встроенная отладка с помощью интерфейса eICE, позволяющего загружать управляющие команды, осуществлять запуск, останов, пошаговое выполнение и использовать точки останова.

- Управление памятью объединяет (для пользователя) внутреннюю и внешнюю память в одну.

- Встроенная Flash-память на 32 Кслов, постраничное стирание, программирование по словам (через eICE).

- Двойные асинхронные порты с программируемой скоростью передачи данных, формированием старта, стопа и четности, а также двойной буферный интерфейс и определение ошибочно принятого кадра.

- Двойные независимые синхронно-асинхронные последовательные порты с поддержкой многих протоколов, в частности, I2C, SPI, Smart Card, Consumer IrDA и заданные пользователем.

- Интерфейс внешнего хоста с поддержкой DMA, 16/32-разрядная шина данных с квитированием связи (снятие головной боли у разработчиков систем связи) и кольцевые буферы.

- 29 битов ввода-вывода общего назначения и параллельного ввода-вывода, каждый из которых конфигурируется отдельно как входной, выходной, с открытым стоком или открытым истоком, и возможностью генерации прерывания по заданному уровню или фронту.

- Два 16-разрядных параллельных порта, которые настраиваются как на вход, так и на выход с открытым стоком или истоком для работы с внешними устройствами.

- Семь 16-разрядных счетчиков-таймеров и один 24-разрядный таймер для больших интервалов времени, каждый из которых формирует прерывания для запуска центрального процессора CPU (рис. 1).

- Интерфейс внешней памяти с поддержкой различных стандартных SRAM и SDRAM для хранения команд и данных.

- 12-разрядный аналого-цифровой преобразователь с частотой выборки 8 кГц, 4-канальным мультиплексором и внутренним (можно использовать и внешний) источником опорного напряжения.

- Встроенный датчик температуры и схема измерения напряжения питания.

- Кварцевый генератор на 32 кГц и 5 МГц с внутренним умножителем до 2,5 МГц и 50 МГц соответственно и алгоритмом автоматического выбора тактовой частоты.

- Управление питанием отдельно для периферийных устройств eCOG1 и ядра (при котором отдельно заданная периферия работает, а центральный процессор находится в спящем режиме.

- Простые в применении программные средства (бесплатные): компилятор ANSI С, макроассемблер, отладчик IСЕ, программа моделирования, а также недорогой стартовый комплект.

- ОС реального времени PicOS (тоже бесплатная).

Поскольку список особенностей eCOG1 не ограничился двумя-тремя пунктами, то рассмотрим наиболее интересные (с нашей точки зрения). Если кого-то заинтересуют другие подробности, то Интернетом: www.cyantechnology.com.

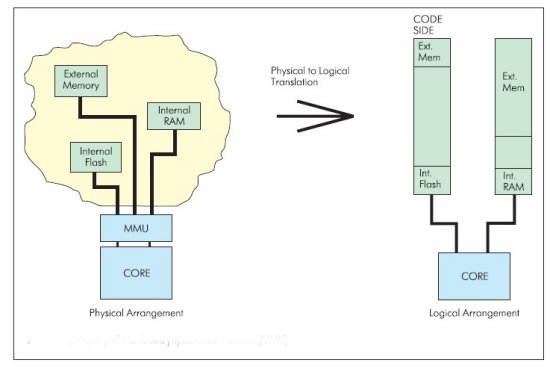

Рисунок 2. Принцип работы блока управления памятью (MMU)

Блок управления памятью (Memory Management Unit – MMU) позволяет представить различные виды внутренней и внешней памяти как одну структуру. Эта структура памяти или модель памяти содержит область команд и область данных в соответствии с архитектурой центрального процессора и обеспечивает преобразование команд для конкретных приложений, а данных – для хранения переменных данных и констант. Для преобразования адресов логической памяти в адреса физической памяти требуется, чтобы почти все компоненты физической памяти начинались с адреса 0х0000. Конфликт адресов устраняется благодаря адресам общей базы памяти и созданию диапазона линейных адресов, а блок управления памятью обеспечивает преобразование адресов логической памяти в адреса физической памяти. Принцип работы MMU представлен на рис. 2 : совокупность всей физической памяти преобразуется в модель памяти, разрабатываемую для конкретного применения.

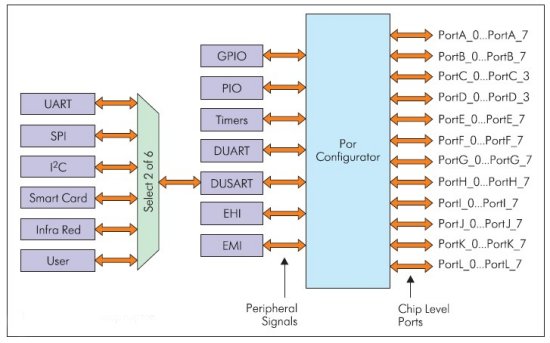

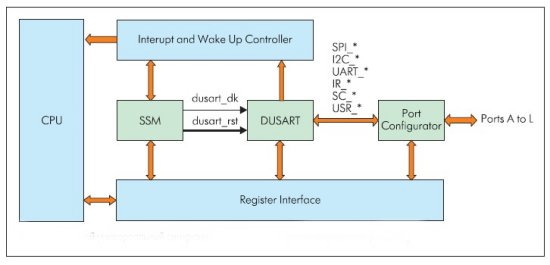

Рисунок 3. Конфигурация портов

Конфигуратор портов используется для выбора сигналов, которые появятся на выходе портов микроконтроллера (рис. 3). Пользователь должен выбрать, какие сигналы от периферии появятся на выводах eCOG1, поскольку eCOG1 содержит больше сигналов, чем выводов. Это позволяет иметь в составе микроконтроллера большое число периферийных устройств, но относительно небольшое число выводов, что позволяет снизить общую стоимость системы. Конфигурируемые выводы сгруппированы в двенадцать портов (PortA…PortL), каждый на 8 или 4 разряда, и обозначаются как PortX_n, где Х – соответствующий порт, а n – номер вывода от 0 до 7. Число конфигураций зависит от порта. В таблице 2 приведены обозначения портов, число выводов для этого порта и количество вариантов конфигурации.

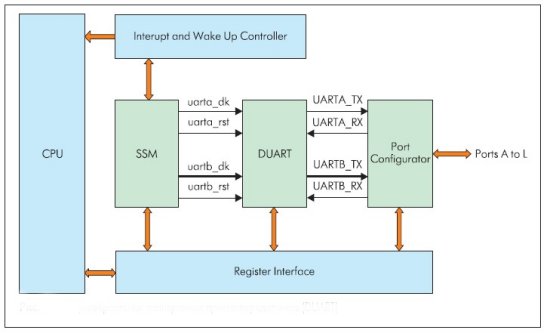

Рисунок 4. Блок универсальных асинхронных приемопередатчиков (DUART)

Таблица 2. Порты eCOG1

| Порт |

Ширина, бит |

Количество конфигураций |

| A |

8 |

10 |

| B |

8 |

6 |

| C |

4 |

8 |

| D |

4 |

4 |

| E |

8 |

4 |

| F |

8 |

4 |

| G |

8 |

4 |

| H |

8 |

4 |

| I |

8 |

4 |

| J |

8 |

4 |

| K |

8 |

4 |

| L |

8 |

4 |

Для каждого порта задается поле в регистре, где выбирается группа сигналов периферийных устройств, которые направляются на соответствующий вывод, а также пара битов установки-сброса для разрешения-запрета работы порта. Если порт закрыт, то его выводы устанавливаются в состояние с высоким импедансом.

Блок универсальных асинхронных приемопередатчиков (DUART) (рис. 4) содержит два отдельных приемопередатчика (каждый со своим 16-разрядным делителем) и имеет следующие особенности:

- Размер кадра состоит из 5, 6, 7 или 8 битов данных, 1, 1,5 или 2 стоповых битов, проверки на четность, нечетность или без нее.

- Автоматическое формирование окончания кадра (от 0 до 64 периодов).

- Определение времени ожидания приема от 1 до 64 периодов.

- Генерация программным способом обрыва строки (15 последовательных нулевых битов данных), детектирование аппаратным методом.

- Программируемый генератор скорости передачи битов от fuart /16 (максимум) до fuart /2 (минимум).

- Прием и передача на одной и той же скорости обеспечивается модулем поддержки системы (SSM).

- 16-разрядные регистры для передачи и приема данных (два кадра данных) с прерываниями, формируемыми при полном и пустом кадре соответственно.

- Определение ошибки приема при сбое стартовых битов совместно с определением сбоев по четности и по кадру.

- Конфигурация полярности данных.

- Предварительная установка тактовой частоты UART для снижения тока потребления.

- Автоматический запуск тактового генератора UART при обнаружении стартового бита и удержание частоты во время передачи данных (снижение энергопотребления).

- Независимая от центрального процессора работа, что позволяет переводить CPU в ждущий режим при передаче или приеме данных.

Следует отметить, что задание параметров кадра необходимо выполнить до использования UART, так как динамически они не могут быть изменены.

Двойной универсальный синхронный асинхронный приемопередатчик (DUSART) представляет собой двойной последовательный порт общего назначения, поддерживающий один из нескольких заданных протоколов с блоком определения, что позволяет программным способом определять простые протоколы последовательной передачи данных. Каждый USART выполнен на двух портах передачи данных и двух портах приема данных (рис.5). Одна пара передачи-приема предназначена для работы в режиме ведущего, вторая – для ведомого.

Рисунок 5. Двойной универсальный синхронный асинхронный приемопередатчик (DUSART)

Аппаратным методом реализованы характеристические функции, общие для контроллеров различных протоколов. Общая часть последовательного порта USART дублируется для каждого канала и доступна для контроллера каждого протокола с помощью матрицы мультиплексоров. Это позволяет без проблем выбирать любой из протоколов для каждого канала. Отметим, что заданный протокол последовательного обмена данных не может использоваться на двух каналах одновременно.

DUSART поддерживает следующие протоколы:

- стандартного UART;

- последовательного периферийного интерфейса (SPI);

- I2C ;

- низкоскоростного IrDA и инфракрасного общего применения (IFR);

- последовательный связной интерфейс ISO 7816 (SCI) для смарт-карт;

- последовательный интерфейс пользователя (USR).

Функциональность двойного универсального синхронно-асинхронного приемопередатчика достигнута благодаря контроллерам протоколов, общим компонентам USART и программному обеспечению пользователя. Программным интерфейсом для DUSART является банк регистров.

Ракович Н.Н.

|