|

Три «С» в одном флаконе (однокристальный аналого-цифровой комплекс Silicon Labs)

Рыночная ниша между микроконтроллерами и аналоговыми приборами всегда была и остается очень заманчивой. И успех здесь приходит к тому (как, впрочем, и везде), кто правильно оценит направление развития этого сектора и вовремя предложит свои изделия.

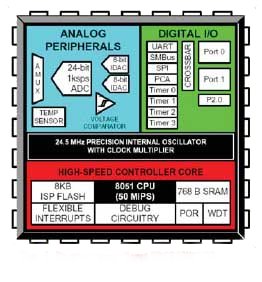

Среди таких успешных компаний на этом рынке – Silicon Laboratories, основное направление деятельности которой – передовые решения в производстве аналого-цифровых приборов. Приобретение фирмы Cygnal значительно расширило гамму выпускаемых приборов, в частности, полную линейку 8-разрядных микроконтроллеров со встроенными аналогово-цифровыми преобразователями, оптимизированными для широкого диапазона применений. Эти ИС объединяют на одном кристалле быстродействующую аналоговую часть, цифровое ядро, флэш-память и порты ввода/вывода, что отражено в рекламном слогане «Capture, Compute, Communicate» (сбор, вычисление и передача данных). Встроенный отладчик значительно облегчает жизнь разработчикам и позволяет сократить сроки производства.

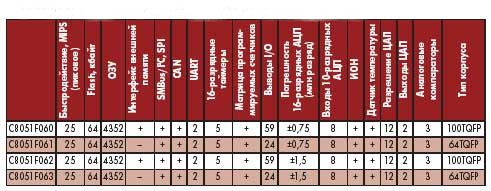

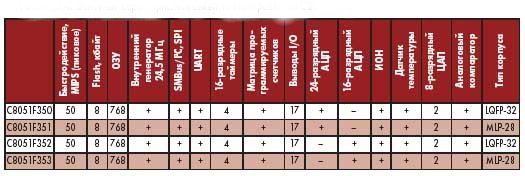

Вся линия микроконтроллеров Silicon Laboratories делится на пять семейств, основные параметры которых приведены в таблице 1.

Таблица 1. Микроконтроллеры Silicon Laboratories

Главные достоинства микроконтроллеров – АЦП высокой точности, высокое быстродействие и низкий уровень шумов.

Топология микроконтроллеров позволила значительно снизить уровень шумов за счет физического разделения всех составляющих: аналоговой, цифровой и интерфейсной.

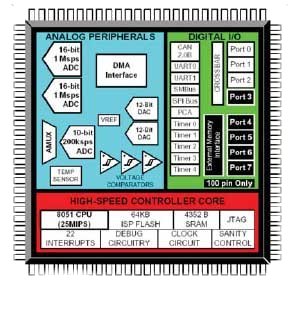

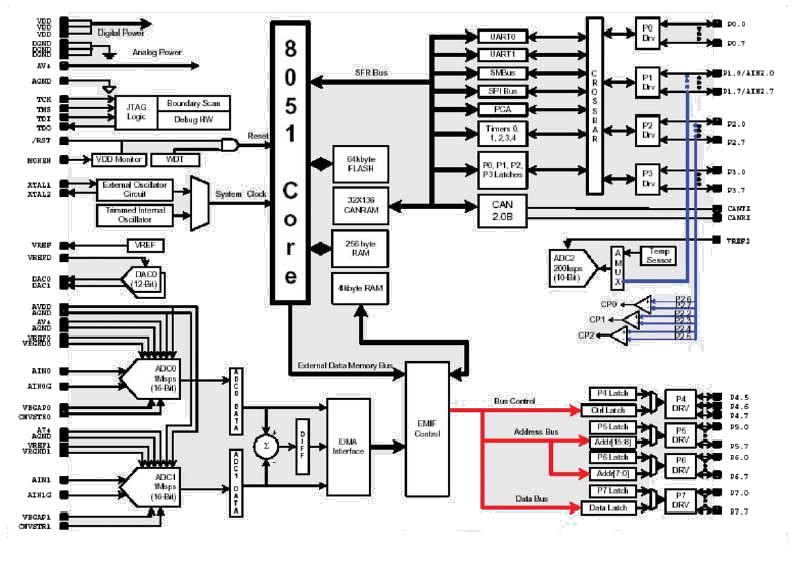

Самое «навороченное» семейство микроконтроллеров – C8051F060/1/2/3 (структура на рис. 1, блок-схема на рис. 2, таблица 2), в состав которого входят: контроллер 8051 на 25 MIPS, CAN 2,0В контроллер, память данных на (4К+256) байт, флэш-память на 64 кбайт, два 16-разрядных АЦП, один 10-разрядный АЦП, два 12-разрядных ЦАП и т.д. Эти т.д. будут рассмотрены ниже.

Рисунок 1. Структура C8051F06x

Рисунок 2. Блок-схема C8051F06x

Таблица 2. Семейство контроллеров C8051F06x (основные характеристики)

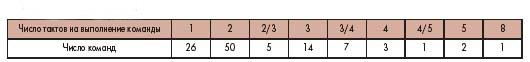

Основа контроллера 8051 – запатентованное ядро CIP-51 фирмы Cygnal, которое полностью совместимо с набором команд MCS-51™ и работает со стандартными ассемблерами и компиляторами 803х/805х. Ядро имеет всю периферию (стандарт 8052), включая пять 16-разрядных счетчиков-таймеров, два дуплексных универсальных асинхронных приемопередатчика (UART), внутреннее ОЗУ на 256 байт, регистр специальных функций на 128 байт и порты ввода/вывода с побитной адресацией. Конвейерная архитектура CIP-51 позволяет значительно повысить быстродействие по сравнению со стандартной архитектурой 8051, в которой все команды (кроме MUL и DIV) выполняются за 12-24 такта при тактовой частоте 12x24 МГц. В ядре CIP-51 70% команд выполняются за один-два такта и только для четырех команд требуется более четырех тактов (таблица 3).

Таблица 3. Число команд

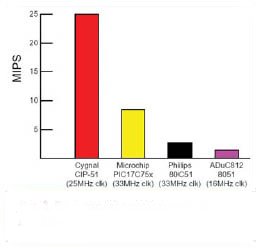

Как следствие, при тактовой частоте 25 МГц пиковая производительность составляет 25 MIPS (сравнение с микроконтроллерами других изготовителей на рис. 3).

Рисунок 3. Сравнительная производительность контроллеров

Для повышения общей производительности и упрощения использования в контроллерах C8051F06х введено несколько важных дополнений.

- Программа обработки прерываний обслуживает до 22 различных прерываний (стандартный 8051 – только 7), что крайне важно при создании многозадачных систем и систем реального времени. Уменьшение обращений к микроконтроллеру со стороны системы управления прерываниями позволило повысить общую производительность.

- Сброс от 7 источников: встроенного монитора питания, сторожевого таймера, детектора пропуска тактов, от компаратора 0 (определение уровня напряжения), принудительный программный сброс, по выводам CNVSTR2 и /RST (двунаправленный). Каждый из сбросов может быть отключен пользователем программным путем, кроме монитора питания и входа сброса /RST.

- Встроенный тактовый генератор, который используется по умолчанию как системный после любого сброса. Возможно переключение «на ходу» на внешний генератор, в качестве которого может применяться кварцевый резонатор, конденсатор, RC-цепь или внешний источник тактового сигнала. Это позволяет ИС работать с низкочастотным внешним генератором (режим пониженного энергопотребления) и при необходимости переключаться на более быстрый внутренний (до 25 МГц) генератор.

Память

Ядро CIP-51 имеет стандартную 8051 адресацию программ и данных. В состав входит 256 байт ОЗУ данных, из них 128 байт с двойной адресацией (прямая и косвенная), 128 байт адресуются только косвенно, регистры специальных функций – только прямая адресация. Помимо стандартной памяти в контроллерах C8051F06х встроен блок дополнительной оперативной памяти на 4 килобайта. Интерфейс внешней памяти (EMIF) оказывается совсем не лишним при работе с внешней памятью данных или периферией с распределенной памятью. Память программ представляет собой флэш-память на 64 килобайта, которая может быть перепрограммирована в системе на сектора по 512 байт, причем для этого не нужно дополнительное внешнее напряжение программирования. Для блокнотной памяти используются отдельные 128 байт.

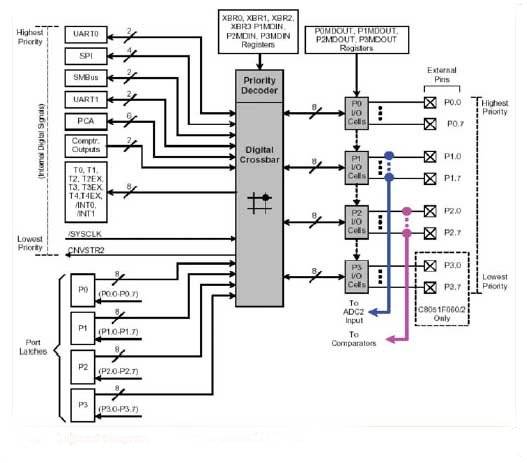

Программируемые порты ввода-вывода (I/O) и цифровой коммутатор

Контроллеры C8051F06х помимо стандартных портов 8051 имеют четыре 8-разрядных порта и один 3-разрядный порт, причем число выводов общего назначения равно 59. Каждый вывод порта I/O можно сконфигурировать как двухтактный или с открытым стоком.

Цифровой коммутатор Digital Crossbat

Наиболее интересной особенностью этого блока ИС является цифровой коммутатор Digital Crossbar (рис. 4).

Рисунок 4. Цифровой коммутатор и порты ввода-вывода C8051F06x

Он представляет собой большую цифровую коммутируемую сеть, которая позволяет распределять потоки данных от внутренних источников на выводы портов ввода-вывода Р0, Р1, Р2 и Р3. В отличие от микроконтроллеров со стандартными мультиплексными портами, цифровой коммутатор реализует все мыслимые (и даже немыслимые) комбинации функций. Сигналы от встроенных счетчиков/таймеров, последовательных шин, аппаратных прерываний, с выходов компараторов и другие сигналы контроллера появляются на выводах портов I/O в той последовательности и в той комбинации, которые определяются Digital Crossbar. Это позволяет разработчику сформировать на выходах I/O то, что необходимо для конкретного приложения.

Матрица программируемых счетчиков

Во всех ИС семейства C8051F06х помимо пяти 16-разрядных счетчиков/таймеров есть и матрица программируемых счетчиков, состоящая из 16-разрядного счетчика/таймера и шести программируемых модулей захвата/сравнения (capture/compare). В качестве тактовых сигналов для базового счетчика/таймера могут быть сигналы от системного тактового генератора (тактовая частота или она же, деленная на 4 или деленная на 12), сигналы переполнения от таймера 0, внешний сигнал (вывод ECI), деленные на 8 тактовые сигналы от внешнего генератора. Каждый из модулей захвата/сравнения можно запрограммировать для работы в одном из шести режимов работы (что значительно расширяет возможности разработчика при одновременном упрощении его работы): захват по фронту сигнала, программный таймер, быстродействующий выход, частотный выход, 8— и 16-разрядный широтно-импульсный модулятор. Подключение модулей к порту ввода-вывода выполняется цифровым коммутатором.

CAN контроллер

На контроллере CAN, который значительно расширяет возможности C8051F06х, подробно останавливаться не будем (информации по CAN более чем достаточно). Ограничимся лишь следующим: возможна работа по протоколу как 2,0А (базовый), так и 2,0В (полный); память сообщений физически отделена от памяти контроллера 8051; поддерживается до 32 объектов сообщений, причем каждый имеет свой идентификатор. Мощное ядро CAN обслуживает все функции протокола по передаче данных и фильтрации сообщений, так что встроенный контроллер 8051 этой работой почти не загружен.

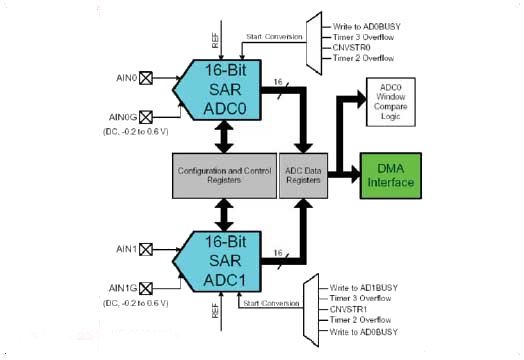

16-разрядные аналого-цифровые преобразователи ADC0 и ADC1

Эти устройства являются одной из ключевых особенностей микроконтроллеров C8051F06х и представляют собой АЦП последовательного приближения с интегрированным блоком слежения-хранения (отсюда и статическая погрешность ±0,75 младшего разряда!) (рис. 5).

Рисунок 5. Блок-схема АЦП C8051F06x

При разрешающей способности 16 бит быстродействие АЦП достигает 106 преобразований в секунду (1Msps). Они могут применяться как раздельно, так и совместно в дифференциальном режиме. В ADC0 и ADC1 реализовано прямое обращение к памяти (внутренней и внешней) посредством интерфейса DMA.

Работают АЦП под управлением контроллера CIP-51 через соответствующие регистры специальных функций. Этот же контроллер может отключить АЦП с целью экономии питания.

Непосредственно аналого-цифровое преобразование запускается одним из четырех способов: программно, по переполнению таймеров 2 или 3, внешним сигналом. ADC0 и ADC1 работают независимо друг от друга, но их можно синхронизировать для одновременного запуска. Результаты преобразования в виде 16-разрядных слов данных хранятся в регистре специальных функций до завершения процесса. Запись данных АЦ-преобразования в память выполняется через интерфейс DMA, что также благотворно сказывается на общем быстродействии.

Для формирования прерывания в случае выхода данных за пределы заданного диапазона в ADC0 имеются регистры Window Compare (окно сравнения). Это позволяет ADC0 постоянно контролировать в фоновом режиме ключевой параметр (например, напряжение) и не выставлять прерывание, пока значение параметра находятся в допустимом окне.

10-разрядный АЦП ADC2

Помимо упомянутых АЦП, в контроллерах C8051F06х есть дополнительный 10-разрядный АЦП ADC2 с разрешением 10 бит и скоростью преобразования 200 ksps. Низкая разрядность (по сравнению с 16-разрядными ADC0 и ADC1) компенсируется входным мультиплексором на 9 входов и усилителем с программируемым коэффициентом усиления. Восемь входов мультиплексора программируются или как отдельные входы, или как дифференциальные. На девятый вход подключен датчик температуры, который часто оказывается совсем не лишним. В остальном (управление от CIP-51, прерывания, окно сравнения) этот АЦП аналогичен ADC0.

Многофункциональность семейства C8051F06х дополняется встроенными двумя 12-разрядными цифро-аналоговыми преобразователями и тремя компараторами, управление которыми выполняется через регистры специальных функций, в том числе и перевод в режим пониженного энергопотребления.

Гистерезис и время отклика компараторов задается программно, а прерывание формируется по фронту сигнала, по спаду или по одному и другому. По этим прерываниям можно вывести контроллер из «спящего» режима, а состояние выходов – опросить программно. Через цифровой коммутатор выход компараторов подключается к портам ввода-вывода.

ЦАП работают в режиме выхода по напряжению и имеют гибкий механизм распределения, благодаря которому выход ЦАП изменяется по команде записи, или по переполнению счетчиков 2, 3 или 4. Кстати, ЦАП довольно часто используются как источники опорного напряжения или напряжения смещения для дифференциальных входов АЦП.

Краткое описание контроллеров C8051F06х будет неполным, если не упомянуть о схеме периферийного сканирования (boundary scan) с 4-проводным интерфейсом JTAG и встроенном отладчике, которые обеспечивают ненавязчивую и быструю отладку непосредственно на готовом изделии. Интерфейс JTAG полностью совместим с IEEE 1149.1.

С помощью встроенного отладчика проверяется и изменяется содержимое памяти и регистров, устанавливаются контрольные и временные точки, проверка стека и пошаговый режим. При этом нет необходимости в дополнительном ОЗУ, памяти программ, таймерах или каналах связи, а режим отладки никак не сказывается на корректности работы всех цифровых и аналоговых устройств C8051F06х. В пошаговом режиме при остановке контроллера 8051 или в точке останова периферия также останавливается (за исключением АЦП и SMBus) для синхронизации с выполняемыми командами. В комплект разработки C8051F060DK входит все программное и аппаратное обеспечение, которое может понадобиться разработчику при работе с C8051F06х: отладчик, интегрированный ассемблер 8051, адаптер RS-232/JTAG, монтажная плата, кабели RS-232 и JTAG, блок питания. Для работы комплекта необходим персональный компьютер с Windows 95/98/NT/ME и один свободный порт RS-232 (рис. 6).

Рисунок 6. Комплект разработки C8051F060DK

Микроконтроллеры семейства C8051F06х – вещь замечательная, но за это надо платить. Если вы готовы поступиться некоторыми «наворотами», не жертвуя быстродействием, то стоит рассмотреть контроллеры семейства C8051F35х (рис. 7), стоимость которых всего 5 долларов.

Рисунок 7. Структура C8051F35x

В таблице 4 приведены основные параметры этого семейства, усиливающие их привлекательность (не стоимостью комплектации жив разработчик).

Таблица 4. Основные характеристики семейства микоконтроллеров C8051F35x

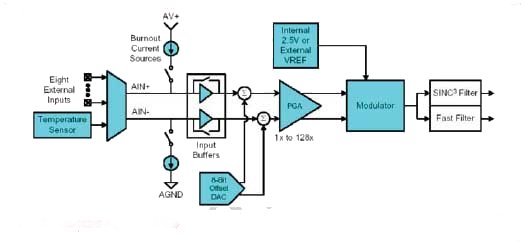

Как и в контроллерах C8051F06х, сильное звено в семействе C8051F35х – аналого-цифровой преобразователь (рис. 8).

Рисунок 8. Блок-схема АЦП C8051F35x

Но здесь это дифференциальный 24— (C8051F350/1) или 16-разрядный (C8051F352/3) сигма-дельта АЦП со встроенной калибровкой. Как следствие – высокая линейность характеристики преобразования. Это объясняется тем, что интегратор сигма-дельта АЦП работает в узком динамическом диапазоне, и нелинейность переходной характеристики усилителя, на котором построен интегратор, сказывается значительно меньше. Емкость конденсатора интегратора у сигма-дельта АЦП составляет десятки пикофарад, так что этот конденсатор формируется прямо на кристалле ИС. В результате сигма-дельта АЦП практически не имеет внешних элементов, что существенно сокращает площадь, занимаемую им на плате, и снижает уровень шумов.

Два отдельных фильтра децимации программируются на полосу до 1 кГц. Источник опорного напряжения 2,5 В – внутренний, но для логометрических измерений возможно применение внешнего дифференциального ИОН. Коэффициент усиления PGA (усилителя с программируемым коэффициентом усиления) задается программно от 1 до 128 за восемь шагов. Внешние сигналы и датчик температуры поступают на дифференциальные входы АЦП через аналоговый мультиплексор. Входные буферы (тоже встроенные) обеспечивают высокий импеданс при прямом подключении внешних датчиков. 8-разрядный ЦАП смещения позволяет проводить коррекцию при большом напряжении смещения на входе.

Наличие двух 8-разрядных ЦАП с выходом по току – стандартная составляющая ИС C8051F35х. Максимальный выходной ток устанавливается на уровне 0,25 мА; 0,5 мА; 1 мА и 2 мА. Гибкий механизм обновления позволяет проводить непосредственную корректировку всей шкалы и поддерживает генерацию сигнала без фазовых искажений. Изменение состояния на выходе ЦАП может выполняться программно, по переполнению таймера или по внешнему сигналу.

Программируемый компаратор – только один (в отличие от трех в C8051F06х), но к возможностям, аналогичным C8051F06х, добавлены два выхода (синхронный «с защелкой» и асинхронный «необработанный»), а также возможность конфигурирования как схемы сброса.

Возможности портов ввода-вывода тоже ограничены – всего 17 выводов, которые организованы как два 8-разрядных порта и один однобитный. Каждый вывод можно сконфигурировать как цифровой или аналоговый, причем в цифровом виде возможна работа в двухтактном режиме или с открытым стоком. Цифровой коммутатор полностью аналогичен C8051F06х.

Выводы

- Быстродействующие и функционально полные контроллеры семейства C8051F06х обеспечивают максимально возможные запросы разработчиков. Единственный недостаток – относительно высокая стоимость.

- Уменьшение функциональных возможностей при сохранении быстродействия позволило значительно снизить стоимость ИС семейства C8051F35х. Более подробную информацию можно найти на сайте www.silabs.com.

Ракович Н.Н.

|