|

Синтез, размещение и трассировка проектов,реализуемых на базе ПЛИС CPLD фирмы Xilinx, в САПР WebPACK ISE

Продолжение. Начало в №№ 6–8’ 2001

После этапа создания нового проекта и модулей исходного описания в соответствии

с методикой, рассмотренной в [1-3], следующий этап процесса разработки цифровых устройств на базе ПЛИС Xilinx® в среде САПР WebPACK™ ISE™ (Integrated Synthesis Environment) — функциональное моделирование. Учитывая, что для этой цели используется система моделирования ModelSim XE Starter™ и программа генерации тестов

HDL Bencher™, описание которых будет представлено в соответствующих публикациях, этапы функционального и временного моделирования будут рассмотрены позже. Поэтому в этой статье мы приступаем к изучению очередной фазы процесса разработки цифрового устройства на базе ПЛИС фирмы Xilinx, которая включает в себя этапы синтеза, размещения и трассировки проекта. Содержание этих этапов различается для семейств CPLD (Complex Programmable Logic Device) и FPGA (Field Programmable Gate Array) [4–7]. Настоящая статья посвящена изучению этапов синтеза и трассировки проекта при использовании ПЛИС семейств CPLD.

Ввод временных и топологических

ограничений проекта

Дополнительная информация для программ синтеза, размещения и трассировки может располагаться непосредственно в модулях исходного описания проекта в форме атрибутов или может быть вынесена в файл временных и топологических ограничений User Constraints File (UCF). Использование файла UCF наиболее предпочтительно, так как при этом сохраняется универсальность модулей исходного описания, которые могут применяться в других проектах. Кроме того, для внесения корректив в параметры ограничений, например при изменении типа ПЛИС, не требуется редактирование различных модулей исходного описания, достаточно лишь скорректировать содержимое файла UCF. Файл временных и топологических ограничений проекта имеет текстовый формат, каждая строка которого представляет собой выражение, описывающее соответствующий параметр. Для внесения информации в файл UCF можно использовать любой текстовый редактор, работающий под управлением операционных систем семейства Windows (по умолчанию используется «Блокнот») или специальную программу Constraints Editor пакета WebPACK ISE, которая на основании данных, указанных разработчиком в диалоговом режиме, автоматически формирует соответствующие выражения для описания ограничений проекта.

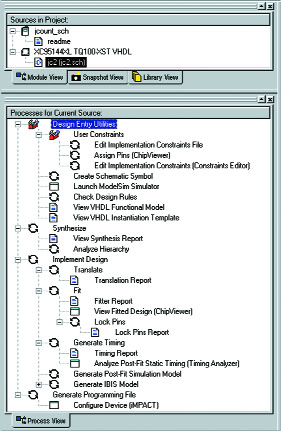

Чтобы приступить к редактированию файла UCF, необходимо в окне исходных модулей Навигатора проекта щелчком левой кнопки мыши выделить строку с названием модуля верхнего уровня иерархии, после чего в окне процессов последовательно развернуть строки «Design Entry Utilities» и «User Constraints» (рис. 1).

Рис. 1. Рабочая область основного окна Навигатора

проекта пакета WebPACK ISE

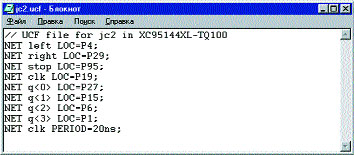

Для изменения файла UCF в текстовом редакторе следует дважды щелкнуть левой кнопкой мыши на строке «Edit Implementation Constraints File», после чего откроется окно редактирования, в котором представлен файл ограничений или его шаблон, создаваемый автоматически для нового проекта. Сохраните файл UCF на диске, чтобы выполненные изменения вступили в силу. Пример открытого в текстовом редакторе файла ограничений для проекта счетчика Джонсона, подготовка которого рассмотрена в [2, 3], показан на рис. 2.

Рис. 2. Пример файла временных и топологических ограничений

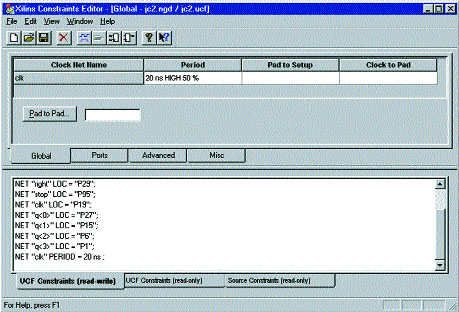

Для модификации файла UCF с помощью редактора временных и топологических ограничений следует дважды щелкнуть левой кнопкой мыши на строке «Edit Implementation Constraints (Constraints Editor)», открыв рабочее окно программы (рис. 3).

Рис. 3. Основное окно редактора временных

и топологических ограничений Constraints Editor пакета WebPACK ISE

В качестве примеров рассмотрим форматы выражений, описывающих наиболее часто используемые ограничения. Параметр LOC позволяет осуществить закрепление выводов перед трассировкой, а также явно указать функциональный блок для реализации элементов проекта. Для привязки «внешних» цепей проекта (подключаемых к контактам кристалла) к требуемым выводам ПЛИС используется следующий формат выражения:

NET <название_цепи> LOC=<номер_вывода_ПЛИС>;

например, NET clock LOC=C5; NET dat1 LOC=P9;

Чтобы определить функциональный блок, внутри которого требуется разместить цепь или элемент проекта, следует воспользоваться соответственно форматами

NET <название_цепи> LOC=FB<номер_функционального_блока_ПЛИС>;

например, NET clock LOC=FB1;

или

INST <обозначение_элемента> LOC=FB<номер_функционального_блока_ПЛИС>;

например, INST D10 LOC=FB2.

Максимальное значение периода сигнала синхронизации для соответствующей цепи проекта задается с помощью параметра

PERIOD. Полный формат выражения ограничения имеет вид

NET <название_цепи_синхронизации> PERIOD=<длительность_периода> [<единицы_измерения>] [{HIGH | LOW}[<длительность_первой_фазы_периода>[<единицы_измерения>] ]],

где значение HIGH или LOW указывает логический уровень сигнала в первой фазе периода. По умолчанию установлены в качестве единиц измерения длительности наносекунды (нс) и одинаковая продолжительность состояний высокого и низкого уровня периода синхросигнала, в результате чего получается сокращенный формат записи:

NET <название_цепи_синхронизации> PERIOD = <длительность_периода>;

например, NET clock PERIOD = 20 нс;

При установке временных ограничений задаваемые значения параметров не должны выходить за рамки предельных норм, которые указаны в справочных данных для выбранного типа ПЛИС.

VHDL-синтез проекта

при использовании средств XST

пакета WebPACK ISE

В процессе синтеза из файлов HDL-описаний проектируемого устройства формируется файл списка соединений в формате EDIF (Electronic Data Interchange Format). Синтезированный файл представляет собой текстовое (ASCII) описание проекта на более низком логическом уровне в формате, воспринимаемом программами трассировки Xilinx. Если исходные описания проекта представлены в графической, в частности схемотехнической форме, то автоматически выполняется их преобразование в требуемый HDL-формат.

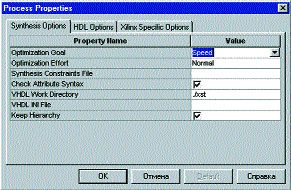

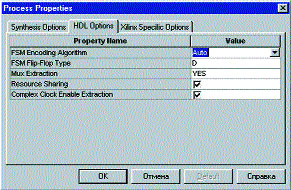

Прежде чем непосредственно активизировать процесс синтеза, следует проконтролировать и при необходимости установить требуемые значения его параметров. В окне процессов щелчком левой кнопки мыши надо выделить строку Synthesize, после чего нажать кнопку на оперативной панели Навигатора проекта или воспользоваться командой Properties контекстно-зависимого всплывающего меню, которое выводится щелчком правой кнопки мыши. В результате выполненных действий на экране монитора отображается диалоговая панель параметров синтеза (рис. 4).

Рис. 4. Диалоговая панель параметров синтеза (страница «Synthesis options»)

Диалоговая панель состоит из трех страниц, снабженных закладками с их названиями: «Synthesis options», «HDL options» и «Xilinx Specific options». Каждая из этих страниц содержит соответствующую группу параметров, представленных в виде таблицы, структура которой подробно рассмотрена в [2, 3]. Для изменения значения параметра следует щелчком левой кнопки мыши активизировать соответствующее поле таблицы, а затем воспользоваться кнопкой управления выпадающим списком значений или, если параметр имеет два состояния (включено/выключено), щелкнуть левой кнопкой мыши на поле индикатора состояния. Содержание страниц диалоговой панели параметров синтеза зависит от выбранного семейства ПЛИС и языка описания HDL. Рассмотрим подробнее параметры синтеза при использовании семейств ПЛИС CPLD и средств XST VHDL.

Рис. 5. Страница «HDL Options»

диалоговой панели параметров синтеза

Страница «Synthesis options» объединяет параметры, управляющие оптимизацией процесса синтеза. Параметр Optimization Goal позволяет выбрать критерий оптимизации и может принимать одно из двух значений: Speed и Area. Speed устанавливает стратегию оптимизации, ориентированную на достижение максимального быстродействия проектируемого устройства. При выборе Area оптимизация выполняется с целью минимизации используемой области (ресурсов) кристалла. По умолчанию установлено значение Speed. Параметр Optimization Effort определяет уровень производимой оптимизации и имеет два возможных значения: Normal — используются стандартные алгоритмы оптимизации и High — выполняется дополнительная оптимизация с учетом особенностей архитектуры выбранного кристалла ПЛИС, что позволяет достигнуть более высоких результатов, но и увеличивает время вычислений. По умолчанию установлено значение Normal. Параметр Synthesis Constraints File определяет название файла ограничений в процессе синтеза, которое может быть введено непосредственно с клавиатуры после активизации поля редактирования значения этого параметра или выбрано при использовании стандартной диалоговой панели открытия файла — кнопка с пиктограммой в виде многоточия («...»). Файл ограничений синтеза (не путать с файлом ограничений проекта UCF) может содержать информацию о параметрах синтеза, которые определяются в рассматриваемой диалоговой панели глобально для проекта в целом, а также о временных и топологических ограничениях, используемых программами трассировки. Учитывая, что ограничения для программы трассировки указываются в файле UCF, а собственно ограничения процесса синтеза чаще всего устанавливаются одинаковыми для всех элементов проекта с помощью диалоговой панели параметров синтеза, можно не указывать значение параметра Synthesis Constraints File. Параметр Check Attribute Syntax позволяет включить или выключить режим проверки синтаксиса атрибутов. При значении «включено», установленном по умолчанию, средства синтеза исключают неопознанные атрибуты (даже если они используются на этапе размещения и трассировки) и выдают соответствующее предупреждение. С помощью параметра VHDL Work Directory указывается название рабочего каталога, в котором сохраняются промежуточные результаты компиляции VHDL-файлов. По умолчанию в рабочей папке проекта средствами синтеза автоматически создается каталог XST. VHDL INI File содержит название INI-файла, в котором устанавливается соответствие VHDL-библиотек для текущего проекта. Параметр Keep Hierarchy определяет возможность сохранения иерархии проекта в процессе синтеза. Если этот параметр установлен в состояние «включено» (маркер на поле индикатора), то объекты, определенные в модулях HDL-описаний, сохраняются в процессе синтеза и не объединяются с остальной частью проекта.

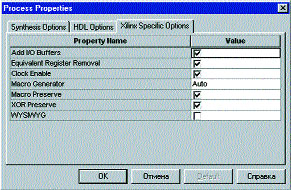

Рис. 6. Страница «Xilinx Specific Options»

диалоговой панели параметров синтеза

Release 4.1WP0.x - xst E.30

Copyright (c) 1995-2001 Xilinx, Inc. All rights reserved.

--> Parameter TMPDIR set to .

CPU : 0.00 / 0.61 s | Elapsed : 0.00 / 1.00 s

. . .

--> Parameter xsthdpdir set to ./xst

CPU : 0.00 / 0.66 s | Elapsed : 0.00 / 1.00 s

--> ======================================================

---- Source Parameters

Input Format : VHDL

Input File Name : jc2.prj

---- Target Parameters

Target Device : XC9500XL

Output File Name : jc2

Output Format : NGC

Target Technology : 9500xl

---- Source Options

Entity Name : jc2

Automatic FSM Extraction : YES

FSM Encoding Algorithm : Auto

FSM Flip-Flop Type : D

Mux Extraction : YES

Resource Sharing : YES

Complex Clock Enable Extraction: YES

---- Target Options

Add IO Buffers : NO

Equivalent register Removal : YES

Macro Generator : Auto

MACRO Preserve : YES

XOR Preserve : YES

---- General Options

Optimization Criterion : Speed

Optimization Effort : 1

Check Attribute Syntax : YES

Keep Hierarchy : YES

---- Other Options

Clock Enable : YES

wysiwyg : NO

============================================================

Compiling vhdl file F:/project/jcount/jc2.vhf in Library work.

Entity <fdc_mxilinx> (Architecture <schematic>) compiled.

. . .

Entity <jc2> (Architecture <schematic>) compiled.

Analyzing Entity <jc2> (Architecture <schematic>).

Set property "keep_hierarchy = TRUE" for instance <dir_reg> in unit <jc2>.

Set property "keep_hierarchy = TRUE" for instance <run_reg> in unit <jc2>.

Set property "keep_hierarchy = TRUE" for instance <jcounter> in unit <jc2>.

Entity <jc2> analyzed. Unit <jc2> generated.

. . .

Analyzing Entity <m2_1_mxilinx> (Architecture <schematic>).

Entity <m2_1_mxilinx> analyzed. Unit <m2_1_mxilinx> generated.

Synthesizing Unit <m2_1_mxilin>.

Related source file is F:/project/jcount/jc2.vhf.

Unit <m2_1_mxilinx> synthesized.

. . .

Synthesizing Unit <jc2>.

Related source file is F:/project/jcount/jc2.vhf.

Unit <jc2> synthesized.

===============================================================

HDL Synthesis Report

Found no macro

===============================================================

Starting low level synthesis...

Optimizing unit <m2_1_mxilinx> ...

. . .

Optimizing unit <jc2> ...

Merging netlists...

===============================================================

Final Results

Output File Name : jc2

Output Format : NGC

Optimization Criterion : Speed

Target Technology : 9500xl

Keep Hierarchy : YES

Macro Preserve : YES

Macro Generation : Auto

XOR Preserve : YES

Design Statistics

# Edif Instances : 58

# I/Os : 8

===============================================================

CPU : 6.87 / 7.53 s | Elapsed : 7.00 / 8.00 s

-->

Рис. 7. Пример отчета о результатах выполнения процесса синтеза

На странице «HDL Options» представлены параметры, управляющие синтезом некоторых объектов HDL-описаний (рис. 5).

Параметр FSM Encoding Algorithm управляет выбором метода кодирования конечных автоматов (Finite State Machine, FSM). Выпадающий список значений содержит восемь элементов:

- Auto, установленное по умолчанию, позволяет средствам синтеза автоматически выбрать для каждого конечного автомата наилучший алгоритм кодирования;

- One-Hot гарантирует, что в любой момент времени активен только один триггер;

- Compact позволяет минимизировать количество триггеров при синтезе конечного автомата;

- Sequential используется метод, заключающийся в идентификации длинных ветвей и применении последовательности двоичных кодов для представления состояний этих ветвей;

- Gray гарантирует переключение только одной переменной между двумя последовательными состояниями, минимизирует риск возникновения паразитных импульсов;

- Johnson целесообразно использовать при синтезе конечных автоматов, описания которых содержат длинные цепочки без ветвлений;

- User указывает средствам синтеза использовать алгоритм кодирования, представленный в файле исходного описания;

- None — запрещается автоматическое кодирование конечных автоматов.

Параметр FSM Flip-Flop Type определяет тип триггеров, используемых при реализации конечных автоматов, и может принимать одно из двух значений: D или T. По умолчанию установлено значение D, предписывающее использование D-триггеров. Mux Extraction разрешает (YES) или запрещает (NO) средствам синтеза извлечение макросов мультиплексоров. По умолчанию установлено значение YES. При этом для каждого обнаруженного описания мультиплексора, выполненного на базе некоторого внутреннего алгоритма, программа синтеза Xilinx Synthesis Technology (XST) формирует макрос или оптимизирует его совместно с остальной частью проекта. Значение Force указывает средствам синтеза игнорировать внутренние алгоритмы и создавать макросы для мультиплексоров. Resource Sharing разрешает или запрещает совместное использование ресурсов арифметическими операторами. По умолчанию используется разрешающее значение. Опция Complex Clock Enable Extraction используется для указания необходимости анализа не только основных шаблонов, но и менее очевидных описаний, где может применяться разрешение синхронизации. Средства синтеза формируют макросы с разрешением синхронизации там, где это возможно. Значение по умолчанию — «включено».

Release 4.1WP0.x - ngdbuild E.30

Copyright (c) 1995-2001 Xilinx, Inc. All rights reserved.

Command Line: ngdbuild -dd _ngo -uc jc2.ucf -p XC9500XL jc2.ngc jc2.ngd

Reading NGO file "F:/project/jcount/jc2.ngc" ...

Reading component libraries for design expansion...

Annotating constraints to design from file "jc2.ucf" ...

Checking timing specifications ...

Checking expanded design ...

NGDBUILD Design Results Summary:

Number of errors: 0

Number of warnings: 0

Writing NGD file "jc2.ngd" ...

Рис. 11. Пример отчета о выполнении

процесса трансляции

Страница «Xilinx Specific Options» содержит параметры синтеза, которые учитывают требования средств трассировки Xilinx (рис. 6).

Параметр Add I/O Buffers разрешает или запрещает автоматическое подключение буферных элементов к цепям модуля исходного описания верхнего уровня проекта, которые предназначены для соединения с выводами кристалла. По умолчанию установлено разрешающее значение.

Если входные и выходные буферные элементы были включены в состав модуля исходного описания проекта на стадии его разработки, то следует изменить значение параметра на «выключено», запрещающее автоматическое подключение этих элементов. Параметр Equivalent Register Removal управляет оптимизацией триггеров в процессе синтеза. При разрешающем значении этого параметра, которое задано по умолчанию, средства синтеза исключают из состава проекта триггеры, выполняющие эквивалентные функции, а также триггеры, входные сигналы которых имеют постоянный уровень, не изменяющийся в процессе функционирования устройства. Clock Enable указывает метод синтеза последовательной логики, использующей сигнал разрешения синхронизации (Clock Enable). Значение «включено», установленное по умолчанию, предписывает использование специальных ресурсов кристалла для ее реализации. В противном случае, при значении «выключено», формируется соответствующая эквивалентная логика. Macro Generator позволяет выбрать средства реализации макросов. Выпадающий список содержит три элемента:

- Macro+ указывает на необходимость использования встроенных средств представления макросов XST;

- LogiBLOX определяет в качестве средств

реализации макросов одноименную программу;

- Auto, установленное по умолчанию, выбирает наиболее оптимальный способ интерпретации макросов.

С помощью параметра Macro Preserve указывается метод синтеза макроописаний, входящих в состав проекта. Значение «включено», установленное по умолчанию для этого параметра, определяет режим сохранения макросов в процессе синтеза и последующую их реализацию с помощью средств генерации Macro+ или LogiBLOX. Значение «выключено» разрешает декомпозицию макросов. Опция XOR Preserve определяет способ синтеза макросов «Исключающее ИЛИ» (XOR). При значении «включено», заданном по умолчанию, макроописания XOR сохраняются в процессе синтеза в виде макросов в формате LogiBLOX, которые реализуются затем одноименными средствами. Такой метод позволяет получить наилучшие результаты с точки зрения минимизации используемых ресурсов. Противоположное значение этого параметра позволяет раскрывать XOR-макросы и затем объединять их с окружающей логикой в процессе синтеза. Параметр WYSIWYG позволяет сохранять в процессе синтеза структуру соединений (все определенные разработчиком сигналы) исходного описания. При этом снижается уровень оптимизации проекта в процессе синтеза. По умолчанию для этого параметра установлено значение «выключено».

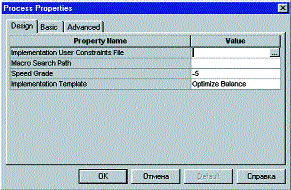

Рис. 8. Диалоговая панель параметров

размещения и трассировки (страница «Design»)

Нажатием клавиши ОК в нижней части диалоговой панели следует подтвердить выполненные изменения параметров синтеза. Двойным щелчком левой кнопки мыши на «Synthesize» в окне процессов Навигатора проекта активизируется процесс синтеза. Информация о ходе его выполнения отображается в окне консольных сообщений. Отмеченное соответствующей пиктограммой в строке Synthesize завершение этого процесса позволяет открыть отчет о результатах синтеза, дважды щелкнув левой кнопкой мыши на строке View Synthesize Report. На рис. 7 приведены фрагменты отчета о выполнении синтеза проекта счетчика Джонсона. Отчет содержит пять основных разделов, выделенных двойной штриховой линией. В разделах указаны:

- Установленные значения параметров синтеза, рассмотренных выше, и некоторых общих параметров проекта (семейство и тип ПЛИС), а также форматы входных и выходных файлов.

- Информация о ходе компиляции и анализе объектов исходных описаний в соответствии с иерархией проекта, а также последовательность их синтеза.

- Данные об обнаруженных макросах.

- Последовательность оптимизации, выполняемой в процессе низкоуровнего синтеза.

- Данные об основных параметрах процесса синтеза и статистические данные полученных результатов — количество EDIF-элементов и блоков ввода/вывода.

После успешного завершения этапа синтеза следует перейти к размещению и трассировке проекта в кристалле ПЛИС.

Размещение и трассировка

проектов, реализуемых на базе

семейств ПЛИС CPLD фирмы Xilinx,

в пакете WebPACK ISE

Этап включает в себя две фазы: трансляция и распределение ресурсов кристалла для реализации проектируемого устройства. В процессе трансляции выполняется объединение всех списков соединений в формате EDIF, входящих в состав проекта, и информации обо всех ограничениях, которая содержится в файлах UCF и NCF(Netlist Constraints File). Результатом трансляции является формирование логического описания проекта в терминах примитивов Xilinx низкого уровня с учетом временных и топологических ограничений, выполненного в формате NGD (Native Generic Database). На второй стадии производится разбиение логического описания проекта на блоки в соответствии с ресурсами выбранного типа ПЛИС. При этом выполняется оптимизация с целью минимизации используемых (необходимых) ресурсов кристалла с учетом заданных ограничений. Результатом этапа размещения и трассировки является создание двоичного файла, который описывает использование физических ресурсов кристалла для реализации функций проектируемого устройства.

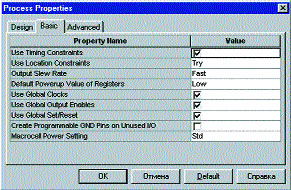

Рис. 9. Страница «Basic» диалоговой панели

параметров размещения и трассировки

Перед активизацией процедур рассматриваемого этапа необходимо установить значения их параметров. Эти значения могут задаваться как отдельно для каждой фазы, например перед ее активизацией, так и единовременно для всего процесса в целом. В первом случае следует выделить в окне процессов (рис. 1) название соответствующей фазы и нажать кнопку на оперативной панели Навигатора проекта или воспользоваться командой Properties контекстно-зависимого всплывающего меню, которое выводится щелчком правой кнопки мыши. В появившейся диалоговой панели нужно установить требуемые значения параметров. При втором способе в окне процессов (рис. 1) выделяется строка с названием этапа «Implement Design» и выполняется та же последовательность действий, что и в первом случае. Рассмотрим подробнее параметры процесса размещения и трассировки. При использовании второго способа диалоговая панель параметров содержит три страницы с закладками: «Design», «Basic», «Advanced» (рис. 8). Установка значений параметров производится теми же методами, что и в диалоговой панели параметров синтеза.

cpldfit: version E.30 Xilinx Inc.

Fitter Report

Design Name: jc2 Date: 12-20-2001, 5:32PM

Device Used: XC95144XL-5-TQ100 Fitting Status: Successful

**************************** Resource Summary ****************************

Macrocells Product Terms Registers Pins Function Block

Used Used Used Used Inputs Used

6 /144 ( 4%) 22 /720 ( 3%) 6 /144 ( 4%) 8 /81 ( 9%) 26 /432 ( 6%)

PIN RESOURCES:

Signal Type Required Mapped | Pin Type Used Remaining

------------------------------------|---------------------------------------

Input : 4 4 | I/O : 5 68

4 4 | GCK/IO : 1 2

Bidirectional : 0 0 | GTS/IO : 2 2

GCK : 0 0 | GSR/IO : 0 1

GTS : 0 0 |

GSR : 0 0 |

---- ----

Total 8 8

MACROCELL RESOURCES:

Total Macrocells Available 144

Registered Macrocells 6

Non-registered Macrocell driving I/O 0

GLOBAL RESOURCES:

Global clock net(s) unused.

Global output enable net(s) unused.

Global set/reset net(s) unused.

POWER DATA:

There are 6 macrocells in high performance mode (MCHP).

There are 0 macrocells in low power mode (MCLP).

There are a total of 6 macrocells used (MC).

End of Resource Summary

***************Resources Used by Successfully Mapped Logic******************

** LOGIC **

Signal Total Signals Loc Pwr Slew Pin Pin Pin

Name Pt Used Mode Rate # Type Use

N35 3 5 FB4_18 STD (b) (b)…

… q <3> 4 5 FB2_5 STD FAST 1 GTS/I/O O

** INPUTS **

Signal Loc Pin Pin Pin

Name # Type Use

clk FB1_14 19 I/O I …

… stop FB4_14 95 I/O I

End of Resources Used by Successfully Mapped Logic

*********************Function Block Resource Summary***********************

Function # of FB Inputs Signals Total O/IO IO

Block Macrocells Used Used Pt Used Req Avail

FB1 1 5 5 4 1/0 11 …

… FB8 0 0 0 0 0/0 10

---- ----- ----- -----

6 22 4/0 81

*********************************** FB1 ***********************************

Number of function block inputs used/remaining: 5/49

Number of signals used by logic mapping into function block: 5

Signal Total Imp Exp Unused Loc Pwr Pin Pin Pin

Name Pt Pt Pt Pt Mode # Type Use

q<1> 4 0 0 1 FB1_8 STD 15 I/O O …

… unused) 0 0 0 5 FB1_18 (b)

Signals Used by Logic in Function Block

1: clk 3: N37 5: "q<2>"

2: N35 4: "q<0>"

Signal 1 2 3 4 Signals FB

Name 0----+----0----+----0----+----0----+----0 Used Inputs

q<1> XXXXX 5 5

0----+----1----+----2----+----3----+----4

0 0 0 0

Legend:

Total Pt - Total product terms used by the macrocell signal …

… Pwr Mode - Macrocell power mode (b) - Buried macrocell

Pin Type/Use - I - Input GCK/FCLK - Global clock

O - Output GTS/FOE - Global 3state/output-enable

…

;;----------------------- Implemented Equations -------------------------;;

… "q<3>" := /"q<0>" * /N37

+ "q<2>" * N37

"q<3>".CLKF = clk

"q<3>".CE = N35

"q<3>".PRLD = GND …

**************************** Device Pin Out ****************************

Device : XC95144XL-5-TQ100

s

G T V T T t T T T T T T V T T T G T T T T T T T T

N I C I I o I I I I I I C I I I N D I I I I I I I

D E C E E p E E E E E E C E E E D O E E E E E E E

--------------------------------------------------

/100 98 96 94 92 90 88 86 84 82 80 78 76\

| 99 97 95 93 91 89 87 85 83 81 79 77 |

q<3> | 1 75 | GND

TIE | 2 74 | TIE

TIE | 3 73 | TIE

left | 4 72 | TIE

VCC | 5 71 | TIE

q<2> | 6 70 | TIE

TIE | 7 69 | GND

TIE | 8 68 | TIE

TIE | 9 67 | TIE

TIE | 10 66 | TIE

TIE | 11 65 | TIE

TIE | 12 64 | TIE

TIE | 13 XC95144XL-5-TQ100 v63 | TIE

TIE | 14 62 | GND

q<1> | 15 61 | TIE

TIE | 16 60 | TIE

TIE | 17 59 | TIE

TIE | 18 58 | TIE

clk | 19 57 | VCC

TIE | 20 56 | TIE

GND | 21 55 | TIE

TIE | 22 54 | TIE

TIE | 23 53 | TIE

T IE | 24 52 | TIE

TIE | 25 51 | VCC

| 27 29 31 33 35 37 39 41 43 45 47 49 |

\26 28 30 32 34 36 38 40 42 44 46 48 50 /

--------------------------------------------------

V q T r T G T T T T T T V T T T T T G T T T T T T

C < I i I N I I I I I I C I I I I I N D I M C I I

C 0 E g E D E E E E E E C E E E E E D I E S K E E

> h

t

Legend : NC = Not Connected, unbonded pin GND = Dedicated Ground Pin

TIE = Tie pin to GND or board trace driven to valid logic level

VCC = Dedicated Power Pin PROHIBITED = User reserved pin

TDI = Test Data In, JTAG pin TDO = Test Data Out, JTAG pin

TCK = Test Clock, JTAG pin TMS = Test Mode Select, JTAG pin

**************************** Compiler Options ****************************

Following is a list of all global compiler options used by the fitter run.

Device(s) Specified : XC95144XL-5-TQ100

Use Timing Constraints : ON …

… Collapsing input limit : 54

Рис. 12. Пример отчета о выполнении размещения и трассировки

Страница «Design» содержит таблицу дополнительных параметров проекта, используемых на этапе реализации. Значение параметра

User Constraints File определяет название используемого файла временных и топологических ограничений. Разработчик может получить несколько вариантов реализации проекта при различных сочетаниях ограничений, подготовив для этого соответствующие файлы UCF. По умолчанию используется файл ограничений со стандартным расширением .ucf, название которого совпадает с именем модуля

исходного описания верхнего уровня иерархии проекта. Изменить значение параметра

User Constraints File можно теми же способами, которые рассмотрены выше для определения названия файла ограничений синтеза. Macro Search Path позволяет указать полное название каталога, в котором находятся описания макросов. Speed Grade используется для определения быстродействия кристалла ПЛИС, выбранного для реализации проекта. Содержание выпадающего списка возможных значений этого параметра зависит от состава ряда градации по быстродействию кристаллов, выпускаемого для ПЛИС выбранного типа. По умолчанию установлено значение, соответствующее максимальному быстродействию выбранного типа ПЛИС. Implementation Template позволяет разработчику выбрать стратегию оптимизации и соответствующие ей параметры процесса размещения и трассировки. Выпадающий список содержит следующие значения:

- Optimize Speed устанавливает критерием оптимизации быстродействие разрабатываемого устройства;

- Optimize Density определяет целью оптимизации достижение максимальной плотности размещения проекта в кристалле (минимизация используемых ресурсов кристалла);

- Optimize Balance, установленное по умолчанию, позволяет сочетать рассмотренные выше стратегии оптимизации.

На странице «Basic» (рис. 9) расположены параметры управления процессом размещения и трассировки, не зависящие от выбранной стратегии оптимизации.

Параметр Use Timing Constraints определяет, будут ли средствами размещения и трассировки приниматься во внимание временные ограничения проекта. При включенном значении этого параметра (используется по умолчанию) оптимизация в процессе размещения и трассировки производится с учетом всех временных ограничений, указанных в модулях исходных описаний проекта и в файлах ограничений UCF и NCF. Если для параметра Use Timing Constraints задано значение «выключено», то средства размещения и трассировки игнорируют всю информацию о временных ограничениях. Параметр Use Location Constraints управляет использованием информации о топологических ограничениях проекта в процессе размещения и трассировки. Выпадающий список возможных значений содержит три элемента:

- Always — процесс размещения и трассировки выполняется с учетом топологических ограничений;

- Ignore — блокирует информацию о топологических ограничениях проекта;

- Try — средства размещения и трассировки пытаются учитывать топологические ограничения, но при отрицательном результате эта информация игнорируется.

Параметр Output Slew Rate предназначен для управления длительностью фронтов выходных сигналов. Выпадающий список доступных значений:

- Fast, установленное по умолчанию, задает режим быстрого переключения выходных сигналов;

- Slow снижает скорость изменения (увеличиваются фронты) выходных сигналов, что позволяет снизить уровень паразитных колебаний (шума) на выходах проектируемого устройства;

- Timing Driven устанавливает скорость переключения выходных сигналов согласно спецификации.

Если в модуле исходного описания или в файле ограничений явно задан режим переключения какого-либо выходного сигнала, то эти данные имеют более высокий приоритет, чем параметр Output Slew Rate.

С помощью параметра Default Powerup Value of Registers определяется состояние регистров (триггеров), устанавливаемое при включении напряжения питания. Значение по умолчанию Low соответствует состоянию логического нуля. Параметр Use Global Clocks управляет использованием глобальных цепей синхронизации. При включенном значении этого параметра, установленном по умолчанию, средства трассировки могут использовать в качестве входов тактовых частот специальные выводы кристалла GCK, подключенные к глобальным цепям синхронизации ПЛИС. Выключенное значение Use Global Clocks запрещает автоматическое использование глобальных тактовых цепей, если только в модулях исходного описания или файле

ограничений явно не указано назначение выводов GCK. Значение параметра Use Global Output Enables разрешает (установлено по умолчанию) или запрещает программам трассировки автоматически использовать глобальные цепи разрешения выходов ПЛИС (выводы GTS) для реализации входов управления тристабильными выходами проектируемого устройства. При запрещающем значении Use Global OutputEnables выводы GTS могут использоваться только при явном указании соответствующих атрибутов в модулях исходного описания проекта или в файлах

ограничений. Use Global Set/Reset управляет использованием вывода GSR, к которому подключены глобальные цепи асинхронной установки и сброса ПЛИС, для реализации соответствующего входа проектируемого устройства. При разрешающем значении этого параметра средства трассировки могут автоматически выбирать вывод GSR в качестве входа асинхронной установки или сброса проектируемого устройства. При установке запрещающего значения программы трассировки используют вывод GSR только при наличии соответствующих атрибутов в модулях исходного описания или файлах ограничений. Параметр Create Programmable GND Pins on Unused I/O позволяет конфигурировать все неиспользуемые выводы ПЛИС как «общий» (GND), что повышает помехоустойчивость проектируемого устройства. По умолчанию установлено значение «выключено». С помощью Macrocell Power Setting указывается режим потребляемой мощности макроячеек кристалла. Выпадающий список значений содержит три варианта:

- Std (задано по умолчанию) соответствует стандартному режиму потребления мощности;

- Low позволяет перевести макроячейки в режим пониженного энергопотребления, что приводит к снижению их быстродействия;

- Timing Driven выбирает режим энергопотребления макроячеек в соответствии с заданными временными ограничениями.

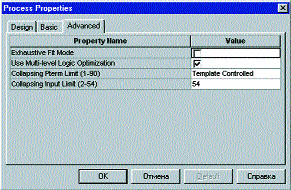

Страница «Advanced» диалоговой панели параметров размещения и трассировки содержит низкоуровневые параметры рассматриваемого процесса (рис. 10). Рекомендуется для них использовать значения, установленные по умолчанию.

Рис.10. Страница «Advanced» диалоговой панели параметров размещения и трассировки

С помощью параметра Exhaustive Fit Mode предоставляется возможность включения режима углубленной компоновки, который позволяет упаковать больший объем логики в выбранный кристалл ПЛИС. По умолчанию этот параметр находится в выключенном состоянии. Use Multi-level Logic Optimization разрешает или запрещает многоуровневую логическую оптимизацию, в процессе которой выполняется упрощение логических выражений, после чего осуществляется преобразование логики в соответствии с выбранным критерием (быстродействие или плотность компоновки). По умолчанию установлено разрешающее значение, позволяющее уменьшить количество уровней логики и минимизировать общее число термов. Значение параметра Collapsing Pterm Limit определяет максимальное количество термов, используемых при реализации сложной комбинаторной логики. Значение по умолчанию определяется выбранной стратегией оптимизации Template Controlled. Параметр Collapsing Input Limit устанавливает максимально допустимое количество входов функционального блока, получающихся в результате разбиения логики. Значение по умолчанию зависит от типа ПЛИС, выбранного для реализации проекта.

Все выполненные изменения параметров размещения и трассировки вступают в силу после нажатия клавиши ОК в нижней части диалоговой панели. Далее следует активизировать процесс размещения и трассировки или поочередно его каждую фазу. Активизация процесса в полном объеме осуществляется двойным щелчком левой кнопки

мыши на строке Implement Design в окне процедур Навигатора проекта (рис. 1). Информация о ходе его выполнения отображается в окне консольных сообщений. Завершение выполнения каждой фазы процесса отмечается соответствующей пиктограммой в строке с ее названием и сопровождается отчетом о полученных результатах. Для просмотра отчета о выполнении трансляции следует дважды щелкнуть левой кнопкой мыши на строке Translation Report. На рис. 11 приведен отчет о выполнении трансляции проекта счетчика Джонсона, синтез которого рассмотрен в предыдущем разделе. Отчет содержит информацию о каждом шаге трансляции (преобразовании EDIF-описаний в формат Xilinx NGD, проверке временных спецификаций, верификации логической структуры проекта), а также об ошибках и предупреждениях.

Чтобы открыть отчет о результатах выполнения размещения и трассировки, следует дважды щелкнуть левой кнопкой мыши на строке Fitter Report. На рис. 12 показан сокращенный вариант отчета о выполнении рассматриваемого процесса для проекта счетчика Джонсона.

Отчет содержит семь основных разделов, в начале каждого из которых указано его название:

- Resource Summary — общая информация о ресурсах ПЛИС и их использовании для реализации проектируемого устройства. В начале этого раздела указаны данные о суммарном количестве и числе используемых макроячеек, термов, регистров, выводов и функциональных блоков кристалла. Далее располагается общая статистическая информация о сигналах, выводах, макроячейках, глобальных ресурсах и режиме потребления макроячеек.

- Resources Used by Successfully Mapped Logic содержит подробную информацию о ресурсах ПЛИС, использованных для реализации проектируемого устройства.

- Function Block Resource Summary — общие статистические данные об использовании функциональных блоков кристалла.

- Подробная информация об использовании ресурсов каждого функционального блока ПЛИС. Этот раздел состоит из N самостоятельных, одинаковых по составу частей с названиями FB1 — FBN, где N — количество функциональных блоков в используемом кристалле.

- Implemented Equations представляет логические выражения, описывающие проектируемое устройство на этапе его реализации.

- Device Pin Out в наглядной форме отражает назначение всех выводов кристалла ПЛИС после загрузки конфигурационных данных проекта.

- Compiler Options содержит значения основных параметров процесса размещения и трассировки.

При получении успешных результатов размещения и трассировки можно перейти к следующим этапам разработки проектируемого устройства.

Литература

- В. Зотов. WebPACK ISE — свободно распространяемый пакет проектирования цифровых устройств на базе ПЛИС Xilinx. Создание нового проекта // Компоненты и технологии. 2001. № 6.

- В. Зотов. WebPACK ISE: Интегрированная среда разработки конфигурации и программирования ПЛИС фирмы Xilinx // Компоненты и технологии. 2001. № 7.

- В. Зотов. Схемотехнический редактор пакета WebPACK ISE. Создание принципиальных схем и символов // Компоненты и технологии. 2001. № 8.

- Д. А. Кнышев, М. О. Кузелин. ПЛИС фирмы «Xilinx»: описание структуры основных семейств. М.: Издательский дом «Додэка-XXI». 2001.

- П. П. Мальцев, Н. И. Гарбузов, А. П. Шарапов, Д. А. Кнышев. Программируемые логические ИМС на КМОП-структурах и их применение. М.: Энергоатомиздат. 1998.

- М. Кузелин. ПЛИС CPLD компании Xilinx с малым потреблением. Серия CoolRunner. // Компоненты и технологии. 2001. № 5.

- М. Кузелин. ПЛИС фирмы Xilinx: семейство Spartan-II. // Компоненты и технологии. 2001. № 3.

Валерий Зотов

walerry@euro.ru

|