|

Однокристальные микроконтроллеры Z80S183 и процессор сигналов от ZiLOG

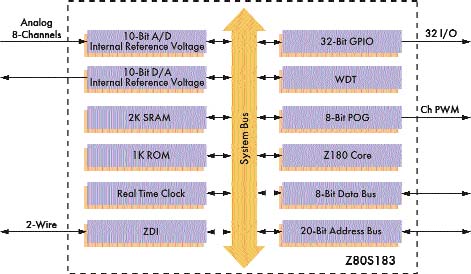

Восьмиразрядный интегральный процессор смешанных сигналов Z183 объединяет на кристалле целый ряд устройств для широкого диапазона встроенных приложений. В то время как большинство восьмиразрядных контроллеров имеют адресное пространство 64 Кбайта памяти программ и данных, у Z183 оно расширено до 1 Мбайта. Основой процессора является популярное ядро Z80S180, в котором повышена производительность и добавлены инструкции для осуществления более эффективной обработки потоков данных. Также поддерживается совместимость с существующими приложениями для Z80. Разработанные ZiLOG пакеты поддержки встроенных web-серверов, поддерживающие протоколы TCP/IP, HTTP и ряд других, обеспечивают для процессора интеграцию в Интернет и возможность разработки сетевых приложений. Эти свойства процессора делают его отличным решением для задач промышленного контроля, автоматизации, удаленного наблюдения, обработки электронных транзакций, модемного и сетевого управления.

В статье рассматриваются функциональные возможности процессора и средства разработки программного обеспечения, в числе которых библиотеки поддержки сетевых протоколов и демонстрационная плата web-сервера на базе Z80S183.

80S183 разработан как интегральный процессор общего назначения. Он состоит из полнофункционального микропроцессора Z80S180, имеет четыре 8-разрядных порта ввода-вывода, 8-канальный АЦП, восемь каналов генератора программируемых выходных сигналов, ЦАП, сторожевой таймер, статическое ОЗУ объемом 2 Кбайта, ПЗУ объемом

1 Кбайт для загрузчика на кристалле, два таймера, а также часы реального времени.

Порты ввода-вывода могут использоваться для общих нужд. Каждая линия программируется независимо на вывод или ввод цифровых сигналов. Выходные ключи поддерживают рабочие токи до

15 мА. Кроме того, линии могут использоваться для специального применения различными устройствами в составе процессора.

В процессоре реализованы три режима пониженного потребления. В режиме STANDBY снимается напряжение с внешнего кварцевого генератора и останавливается внутренний тактовый генератор; потребляемый ток уменьшается до 10 мкА. Переходя в режим SLEEP, процессор останавливается в определенном состоянии, при котором работают только устройства ввода-вывода. В режиме SYSTEM STOP прекращается работа и этих устройств, и потребление снижается далее.

Периферийные устройства

Два скоростных УАПП. Благодаря наличию задающего генератора, заимствованного у коммуникационных контроллеров серии Z182, два асинхронных приемо-передатчика обеспечивают скорость обмена до 512 Кбод. Приемный модуль УАПП имеет FIFO-буфер объемом 4 байта, снижающий вероятность ошибок переполнения.

Два ПДП. Каналы прямого доступа к памяти (ПДП) поддерживают попеременное подключение к источнику при работе с одним внешним устройством. Это свойство позволяет двум каналам обслуживать внешнее устройство, снижая долю участия процессора в передаче данных.

Два счетчика-таймера. Два 16-разрядных таймера ведут счет от заданного значения и имеют свойство начинать счет вновь с начального значения при достижении нулевой величины в счетчике. Один таймер поддерживает управление логическим выходом процессора и может быть использован как модулятор.

Синхронный интерфейс. Блок последовательного синхронного интерфейса (CSIO) управляет работой приемника и передатчика в полудуплексном режиме. Интерфейс служит простым средством

организации высокоскоростной связи с другими процессорами.

Программируемый генератор. Это устройство в составе Z80S183 представляет собой генератор событий. Согласно специальной программе, записываемой в оперативную память процессора, блок создает выходные сигналы заданной формы, управляет запуском АЦП и ЦАП и генерирует прерывания процессора. События следуют с высокой частотой, вследствие чего обеспечивается высокая производительность. Вмешательство процессора в работу генератора минимально.

ZiLOG Debug Interface (ZDI) — отладочный интерфейс, используемый для внутрисхемной эмуляции работы процессора. ZDI позволяет пользователю посредством отладочного устройства выполнять программу процессора в пошаговом режиме, получать данные о регистрах и содержимом памяти и изменять их.

Характеристики процессора:

- Макроядро Z80S180. Его свойства:

- повышенная производительность CPU. Совместимость с ядром Z80, расширенный набор команд;

- диапазон рабочих частот до 33 МГц;

- рабочее питание 3,3 и 5 В;

- два канала DMA;

- два скоростных асинхронных последовательных интерфейса;

- два 16-разрядных таймера;

- синхронный последовательный интерфейс;

- блок управления памятью на кристалле

(1 Мбайт);

- контроллер прерываний, по уровню и по фронту;

- генератор задержек на шине;

- режимы низкого потребления;

- режимы сниженных наводок;

- 32 линии ввода-вывода общего назначения;

- 8-канальный 10-разрядный АЦП;

- 10-разрядный ЦАП;

- 8-разрядный программируемый модулятор;

- статическое ОЗУ объемом 2 Кбайт;

- ПЗУ объемом 1 Кбайт на кристалле — виртуальный загрузчик;

- часы реального времени;

- маломощный фазовый генератор;

- сторожевой таймер;

- экономичный 100-выводной корпус.

| MMU |

WDT |

PLL |

| 24 I/O |

z180 |

2 T/C |

| 2 UART |

RTC |

| CSICO |

1K ПЗУ |

| ZDI |

2 DMA |

2K СОЗУ |

| 8 АЦП |

ЦАП |

POG |

Демонстрационная плата

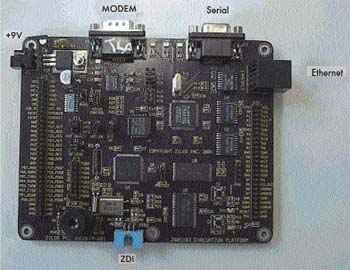

Оценить по достоинству все свойства процессора позволяет разработанная ZiLOG демонстрационная плата. Плата оснащена двумя банками памяти — 1 Мбайт ОЗУ и

1 Мбайт Flash. Размещенный на плате модуль MAC на базе чипа CrystalLAN обеспечивает плату коммуникационным интерфейсом Ethernet. Два асинхронных последовательных интерфейса процессора могут использоваться как модем и как консоль для подключения удаленных терминалов. Другие периферийные устройства в составе Z80S183 доступны для пользователя посредством ряда коннекторов по бокам платы. На эти коннекторы разработчик может устанавливать свои функциональные модули для передачи сигналов на процессор. Впоследствии коммуникационные свойства процессора можно использовать для передачи обработанных сигналов в Интернете или вывода отчетов на терминал.

Рис. 1. Структурная схема процессора Z80S183

ZiLOG разработал полный стек семейства протоколов TCP/IP. Поддерживаются протоколы HTTP, FTP, SMTP, SNMP, DHCP, PPP и ряд других, благодаря которым плата может использоваться как web-сервер на базе однокристального микроконтроллера. Стек обеспечивает одновременную обработку не менее четырех клиентских запросов к web-серверу; соединения устанавливаются посредством открытия сокетов. Другая версия TCP/IP стека для микроконтроллера 80S183 — CMX-Micronet — разработана компанией CMX — известным производителем сетевого программного обеспечения.

Рис. 2. Демонстрационная плата разработчика на Z80S183

На плате имеется разъем для подключения к отладочному интерфейсу ZDI. В стандартной конфигурации комплекта разработчика ZiLOG этот разъем используется для подключения модуля отладки ZPak. Этот модуль служит для соединения платы с персональным компьютером, на котором установлена среда разработчика ZiLOG Development Studio (ZDS). Программа доступна для свободного использования на web-сайте компании. Проекты ZDS позволяют включать файлы гипертекста *.html. Разработав содержимое web-сайта, достаточно разместить его в составе проекта, после чего оно автоматически преобразуется при компиляции в загружаемый код и копируется в память демонстрационной платы вместе с программным обеспечением процессора. Сразу после загрузки web-сервер становится доступным в сети. После регистрации в службе доменных имен к серверу на базе Z80S183 можно обращаться по имени из Интернета.

Автором статьи разработана библиотека загрузки программного обеспечения во Flash-память демонстрационной платы — Z183 Flash Loader. Библиотека имеет в своем составе модуль пользовательского интерфейса. На экране терминала отображается меню функций, позволяющих записать программу пользователя в ПЗУ платы. При этом другого аппаратного обеспечения, кроме терминального компьютера и демонстрационной платы, не требуется. Flash Loader позволяет таким образом заменять программное обеспечение платы или загружать его новые версии в «полевых» условиях при наличии мобильного терминала.

Ссылки на ресурсы

|